# Técnicas de procesamiento coherente de señales: implementación y aplicaciones en instrumentación

Tesis de Doctorado en Ingeniería

### Matías Javier Oliva

Director de tesis: Pablo Andrés García Co-director de tesis: Alejandro Luis Veiga

Facultad de Ingeniería Universidad Nacional de La Plata

## Resumen

La medición de señales de amplitudes pequeñas inmersas en ruido es un problema común en instrumentación electrónica, que aparece en áreas tan diversas como las telecomunicaciones, la bioingeniería o el control automático. Las técnicas a aplicar para posibilitar estas mediciones son muy variadas y dependen de la señal que se desee detectar y la naturaleza del ruido asociado. En particular, si la señal es periódica o puede ser modulada a una frecuencia determinada las técnicas de detección o demodulación coherente se presentan como una buena solución. Existe una gran variedad de estas técnicas, que aprovechan el conocimiento de la periodicidad de la señal para diferenciarla del ruido circundante. Entre estas técnicas destacan la amplificación Lock-in y la promediación coherente, las cuales han recibido especial atención tanto por la relativa simplicidad de su implementación como por los buenos resultados que permiten obtener. En la actualidad existen dispositivos comerciales que efectúan este tipo de mediciones, pero tienen la desventaja de ser costosos y voluminosos, bien adaptados para su uso en entornos controlados de laboratorio, pero no para aplicaciones embebidas y portables.

El desarrollo de sistemas de detección coherente de bajo costo, portables y bien diseñados para su integración con dispositivos funcionales se ha identificado como un problema con diversas aplicaciones. En este punto se destacan tres por su relevancia en esta tesis, aunque el abanico de casos es mucho más amplio. Estas son: la Tomografía Magnética para la detección de nanopartículas ferromagnéticas en técnicas de terapias oncológicas, el desarrollo de interfaces cerebro computadora basadas en estímulos visuales periódicos y la instrumentación de sistemas de Espectroscopía Mössbauer. El primer capítulo de esta tesis se encarga de presentar estas aplicaciones y justificar la utilidad de las técnicas de detección coherente para su implementación.

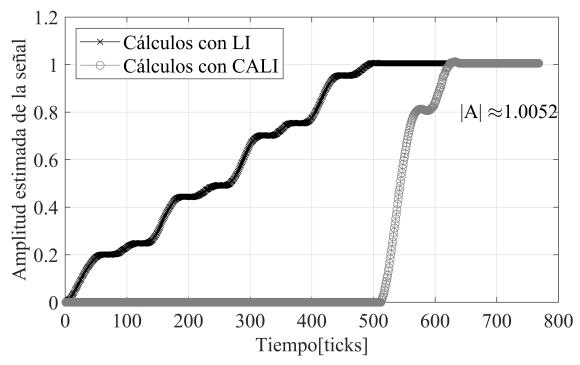

Con el fin de desarrollar estas aplicaciones se han explorado en detalle los aspectos teóricos de las técnicas de *Lock-in* y promediación coherente y se ha evaluado cómo se pueden combinar para lograr dispositivos eficientes. En este sentido se ha determinado que, bajo ciertas circunstancias, combinar las técnicas de promediación coherente y *Lock-in* proporciona los mismos resultados que usar esta última individualmente. Luego, esta propiedad se ha utilizado para minimizar la cantidad de multiplicaciones involucradas en los cálculos, contribuyendo a mejorar la eficiencia de los algoritmos. La revisión detallada de los aspectos teóricos de estas técnicas y la derivación del algoritmo resultante, bautizado CALI, puede encontrarse en el segundo capítulo de esta tesis.

Luego del estudio de los aspectos teóricos de la detección coherente se aborda su implementación, para su posterior aplicación en los contextos planteados. La implementación tiene estrictos requerimientos de tiempo real, lo que es difícil de cumplir con microprocesadores tradicionales, especialmente cuando la frecuencia de la señal es elevada. Es por esto que las implementaciones exploradas incorporan el procesamiento digital de la señal en lógica programable. El desarrollo de sistemas basados en dispositivos de este tipo lleva aparejados una gran cantidad de desafíos que se han intentado simplificar a lo largo de esta investigación. En este sentido, se ha desarrollado un

sistema reutilizable de procesamiento de señales de código abierto, que se ha probado en sistemas de lógica programable de distintos fabricantes. El desarrollo de este sistema reutilizable de señales comprende el tercer capítulo de esta tesis.

A partir de este sistema reutilizable se han diseñado e implementado sistemas de detección coherente de señales en distintos dispositivos de lógica programable. Utilizando lo estudiado previamente, se han diseñado estas herramientas de forma eficiente, mediante una combinación de las técnicas de *Lock-in* y promediación coherente. La descripción de estos diseños y su caracterización se puede encontrar en el cuarto capítulo de esta tesis.

En el quinto capítulo se describe cómo los dispositivos desarrollados se utilizaron en las aplicaciones propuestas. Estos logran solucionar algunos de los desafíos inherentes de cada aplicación, proveyendo equipos embebidos y portables. En el campo de la Tomografía Magnética se ha logrado predecir la posición de las partículas ferromagnéticas en elementos de prueba, reemplazando a un Lock-in comercial, voluminoso y difícilmente trasladable utilizado en implementaciones anteriores, acelerando además el proceso de medición. En el campo de las interfaces cerebro computadora se ha logrado detectar la atención del usuario a tres estímulos visuales distintos, sin que éste realice acciones motoras, utilizando amplificación Lock-in. A diferencia de esta propuesta, la mayoría de los trabajos previos recurren a la Transformada de Fourier, lo que representa una solución menos eficiente. Finalmente, en el campo de la Espectroscopía Mössbauer se han utilizado los sistemas desarrollados para optimizar el proceso de calibración de los equipos, mejorando la calidad de los espectros obtenidos y reemplazando el uso del osciloscopio en la promediación coherente, que ahora se realiza de forma más simple y automatizada. En todos los casos se destaca la flexibilidad y escalabilidad de los dispositivos implementados.

Finalmente, en el sexto capítulo se enumeran las principales conclusiones de este trabajo de investigación, resaltando los logros alcanzados y las limitaciones encontradas a lo largo de su desarrollo. Además, se explora el trabajo a futuro que surge de este estudio. Se presentan varios aspectos que quedan por profundizar, tanto en las aplicaciones prácticas como en los aspectos teóricos, por lo que esta investigación sirve como un punto de partida para diversas líneas de trabajo.

# Índice general

| 1        | $\operatorname{Intr}$ | troducción                                                   |  |  |  |  |

|----------|-----------------------|--------------------------------------------------------------|--|--|--|--|

|          | 1.1.                  | Sistemas de detección coherente                              |  |  |  |  |

|          | 1.2.                  | Dispositivos SoC-FPGA                                        |  |  |  |  |

|          | 1.3.                  | Técnicas tomográficas para detección de nanopartículas       |  |  |  |  |

|          |                       | 1.3.1. Hipertermia Magnética                                 |  |  |  |  |

|          |                       | 1.3.2. Tomografía Magnética                                  |  |  |  |  |

|          |                       | 1.3.2.1. Fundamentos                                         |  |  |  |  |

|          |                       | 1.3.2.2. Determinación de los parámetros de operación        |  |  |  |  |

|          |                       | 1.3.2.3. Medición de la tensión en la espira sensora         |  |  |  |  |

|          | 1.4.                  | Interfaces cerebro computadora                               |  |  |  |  |

|          | 1.5.                  | Espectroscopía Mössbauer                                     |  |  |  |  |

|          | 1.6.                  | Propuesta para un sistema de detección coherente en SoC-FPGA |  |  |  |  |

|          | 1.7.                  | Resumen de publicaciones producidas                          |  |  |  |  |

|          |                       | 1.7.1. Trabajos publicados en revistas                       |  |  |  |  |

|          |                       | 1.7.2. Trabajos publicados en congresos                      |  |  |  |  |

|          |                       | 1.7.3. Repositorios de código abierto                        |  |  |  |  |

|          | 1.8.                  | Estructura de la tesis                                       |  |  |  |  |

| <b>2</b> | Téc                   | nicas de detección coherente 18                              |  |  |  |  |

| _        | 2.1.                  | Introducción                                                 |  |  |  |  |

|          | 2.2.                  | Lock-in                                                      |  |  |  |  |

|          |                       | 2.2.1. <i>Lock-in</i> de una fase                            |  |  |  |  |

|          |                       | 2.2.2. <i>Lock-in</i> de dos fases                           |  |  |  |  |

|          |                       | 2.2.3. Análisis en el Dominio Complejo                       |  |  |  |  |

|          |                       | 2.2.4. Efecto sobre el ruido blanco                          |  |  |  |  |

|          |                       | 2.2.5. Elección del filtro pasa-bajos                        |  |  |  |  |

|          |                       | 2.2.5.1. Filtro de media móvil                               |  |  |  |  |

|          |                       | 2.2.5.2. Filtros de respuesta impulsional infinita (IIR)     |  |  |  |  |

|          |                       | 2.2.6. Efecto del ruido de cuantización                      |  |  |  |  |

|          |                       | 2.2.6.1. Caso $f_m = K f_s$                                  |  |  |  |  |

|          |                       | 2.2.6.2. Caso $f_m \neq K f_s$                               |  |  |  |  |

|          |                       | 2.2.6.3. Resumen                                             |  |  |  |  |

|          |                       | 2.2.7. Caso $f_s = 100 \text{ kHz}$                          |  |  |  |  |

|          |                       | 2.2.8. Antecedentes                                          |  |  |  |  |

|          | 2.3.                  | Promediación coherente                                       |  |  |  |  |

|          |                       | 2.3.1. Fundamentos                                           |  |  |  |  |

|          |                       | 2.3.2. Antecedentes 41                                       |  |  |  |  |

4 ÍNDICE GENERAL

|   | 2.4. | Combinación de promediación coherente y <i>Lock-in</i>                       |

|---|------|------------------------------------------------------------------------------|

|   |      | 2.4.1. Formulación matemática                                                |

|   |      | 2.4.1.1. Conceptos generales                                                 |

|   |      | 2.4.1.2. Aproximación intuitiva                                              |

|   |      | 2.4.1.3. Demostración formal                                                 |

|   |      | 2.4.1.4. Número de operaciones                                               |

|   |      | 2.4.1.5. Simulaciones                                                        |

|   | 2.5. | Conclusiones                                                                 |

| 3 | Pro  | cesamiento de señales en SoC-FPGA 51                                         |

|   |      | Introducción                                                                 |

|   | 3.2. |                                                                              |

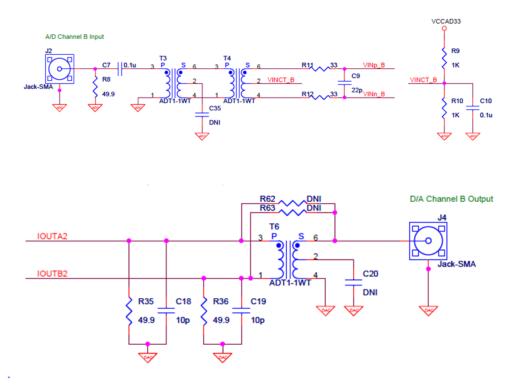

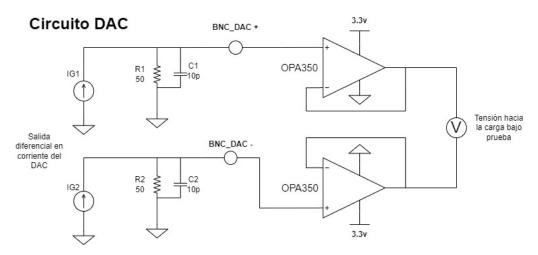

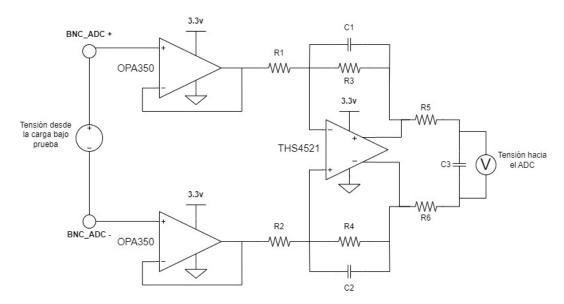

|   |      | 3.2.1. Placa de expansión <i>Highspeed AD/DA daughter card</i> (ADA-GPIO) 53 |

|   |      | 3.2.2. Acoplamiento en continua de la placa Highspeed AD/DA Card 54          |

|   | 3.3. | Sistema reutilizable de procesamiento de señales                             |

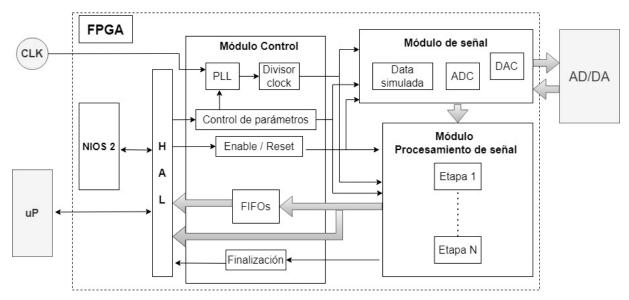

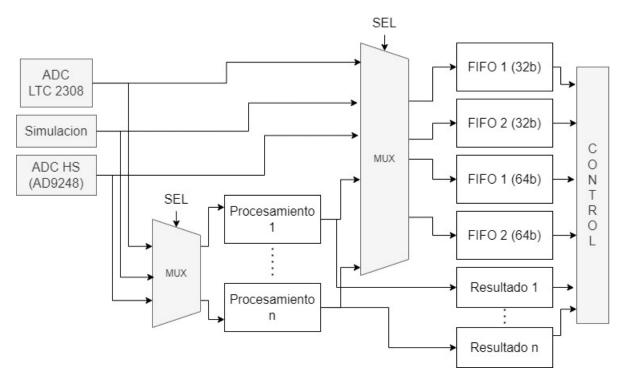

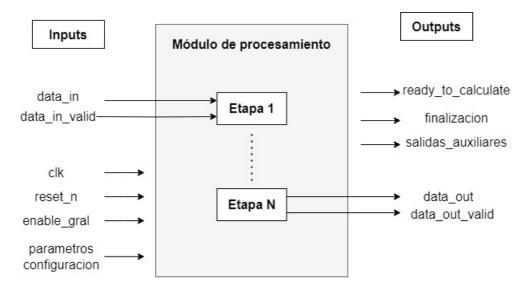

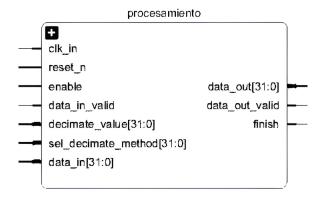

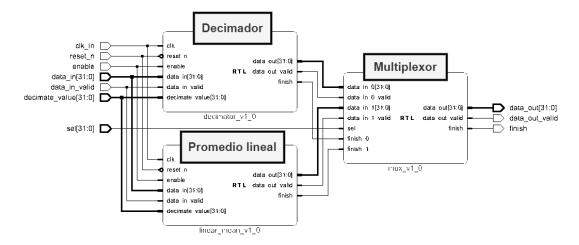

|   | 0.0. | 3.3.1. Esquema general del diseño                                            |

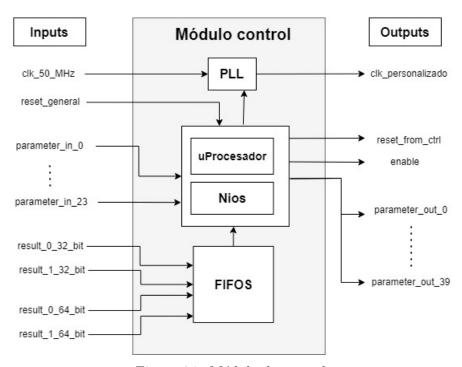

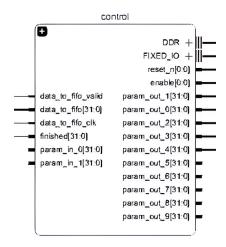

|   |      | 3.3.2. Etapa de control                                                      |

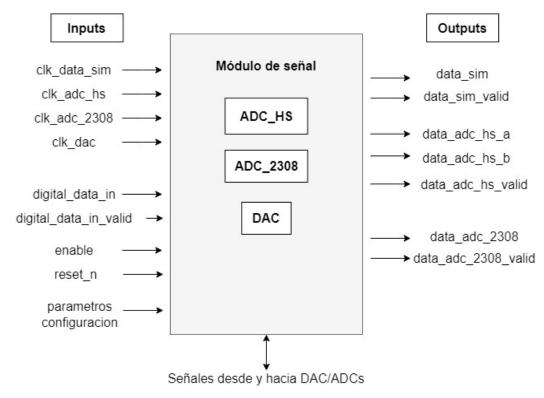

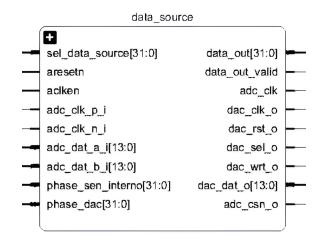

|   |      | 3.3.3. Etapa de fuente de señal                                              |

|   |      | 3.3.3.1. Señal digital                                                       |

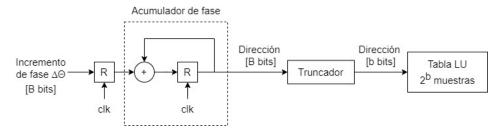

|   |      | 3.3.3.2. Síntesis digital directa por truncamiento de fase 62                |

|   |      | 3.3.3.3. Generación de secuencias pseudo-aleatorias                          |

|   |      | 3.3.3.4. Controlador del ADC High-Speed                                      |

|   |      | 3.3.3.5. Controlador del DAC High-Speed                                      |

|   |      | 3.3.3.6. Controlador del ADC LTC 2308                                        |

|   |      | 3.3.4. Etapa de procesamiento de señal                                       |

|   |      | 3.3.4.1. Filtros de respuesta impulsional finita                             |

|   | 3.4. |                                                                              |

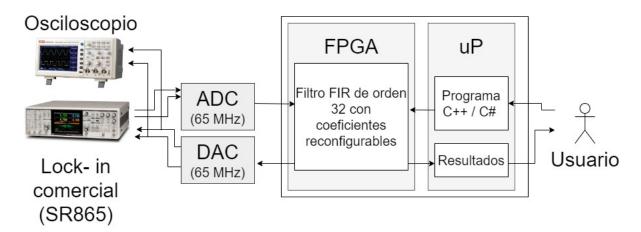

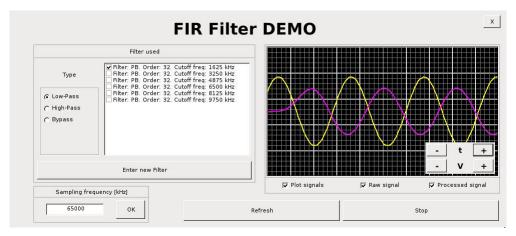

|   | 0.1. | 3.4.1. Resultados                                                            |

|   |      | 3.4.1.1. Recursos utilizados                                                 |

|   |      | 3.4.1.2. Mediciones temporales                                               |

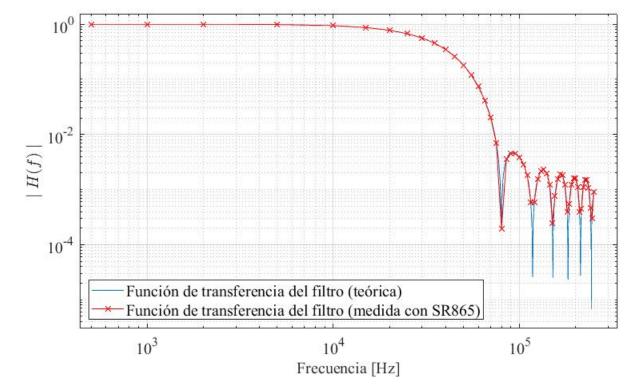

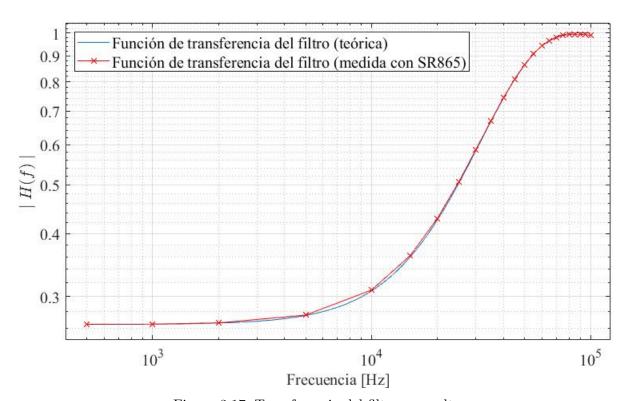

|   |      | 3.4.1.3. Respuesta del filtro FIR                                            |

|   | 3.5. | •                                                                            |

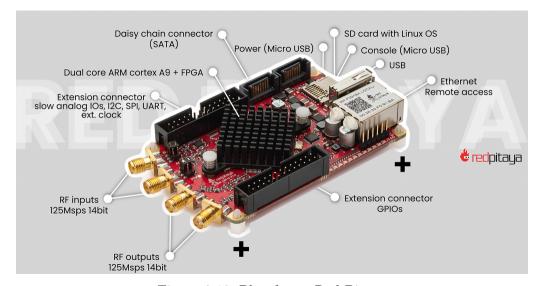

|   | 0.0. | 3.5.1. Red Pitaya                                                            |

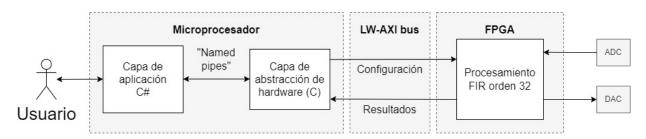

|   |      | 3.5.2. Implementación                                                        |

|   |      | 3.5.3. Uso de recursos y temporización                                       |

|   |      | 3.5.4. Filtro pasa-bajos                                                     |

|   | 3.6. |                                                                              |

|   | ъ.   |                                                                              |

| 4 |      | ección coherente en SoC-FPGA 77                                              |

|   | 4.1. | Introducción                                                                 |

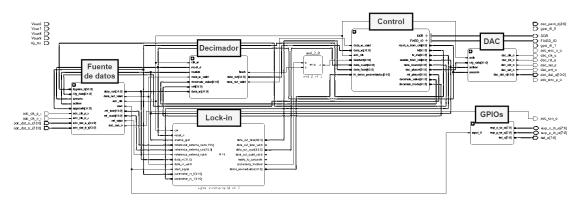

|   | 4.2. | Implementación del sistema en DE1-SoC                                        |

|   |      | 4.2.1. Hardware                                                              |

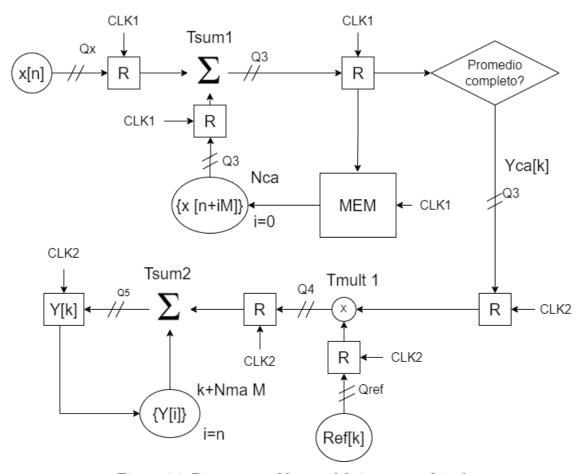

|   |      | 4.2.1.1. Promediación coherente                                              |

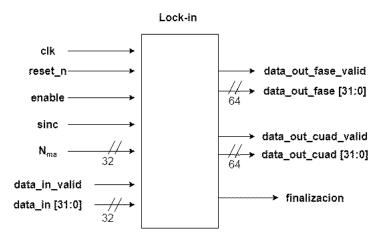

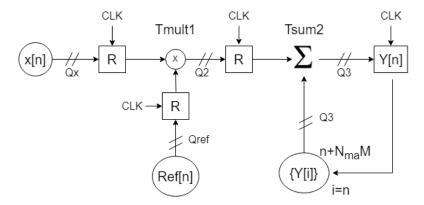

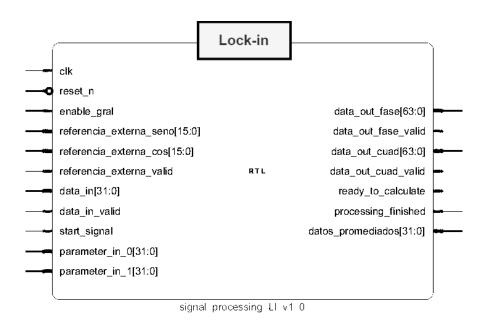

|   |      | 4.2.1.2. Lock-in                                                             |

|   |      | 4.2.1.3. Combinación de promediación coherente y <i>Lock-in</i>              |

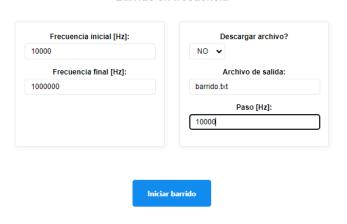

|   |      | 4.2.2. Interfaz de usuario                                                   |

|   |      | 4.2.2.1. Programas base para el sistema de detección coherente               |

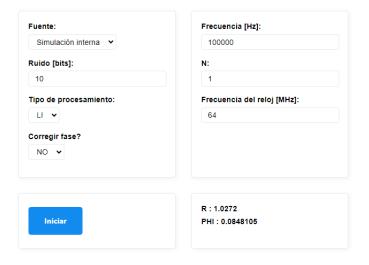

|   |      | 4.2.2.2. Servidor web                                                        |

ÍNDICE GENERAL 5

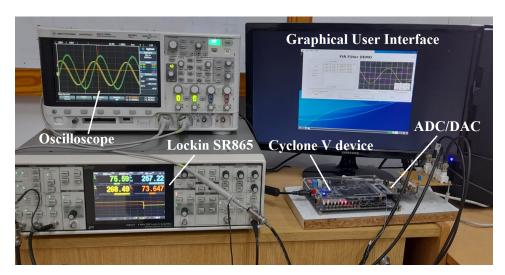

|          | 4.3.           | ados en De1-SoC                | 89                                                                         |     |  |  |

|----------|----------------|--------------------------------|----------------------------------------------------------------------------|-----|--|--|

|          |                | 4.3.1.                         | Tiempo individual de operaciones                                           | 89  |  |  |

|          |                | 4.3.2.                         | Uso de recursos de cada algoritmo                                          | 90  |  |  |

|          |                | 4.3.3.                         | Implementación del sistema de detección coherente                          | 90  |  |  |

|          |                |                                | 4.3.3.1. Consideraciones temporales                                        | 90  |  |  |

|          |                |                                | 4.3.3.2. Uso de recursos del sistema completo                              | 92  |  |  |

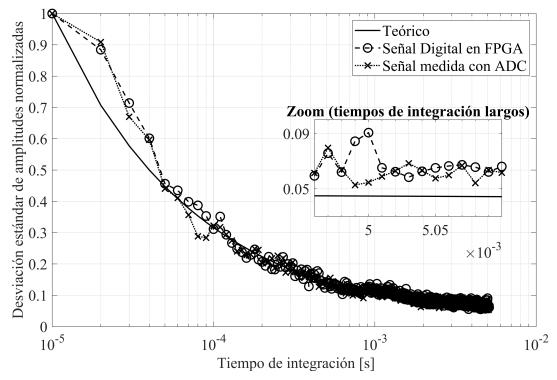

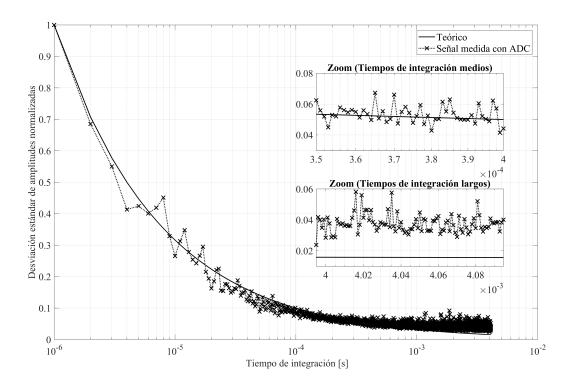

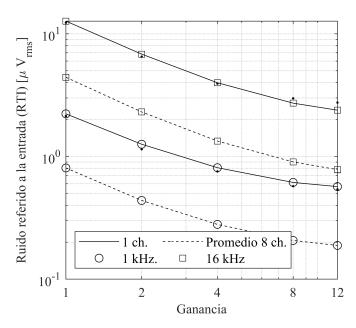

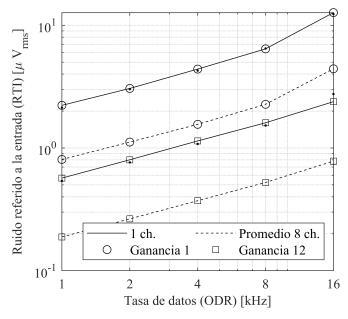

|          |                |                                | 4.3.3.3. Mediciones de Ruido                                               | 92  |  |  |

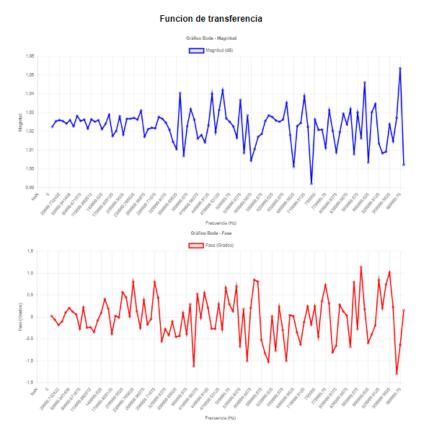

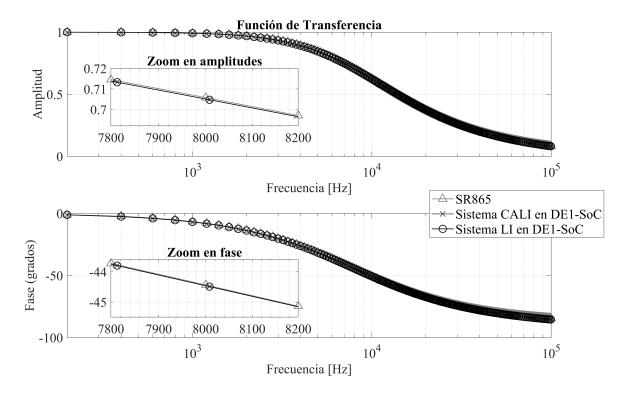

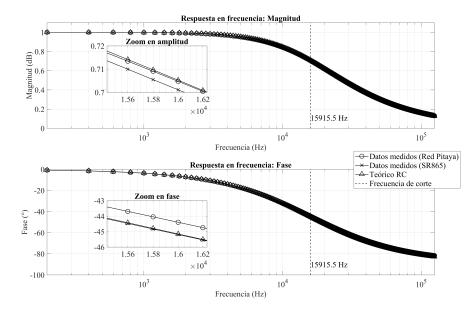

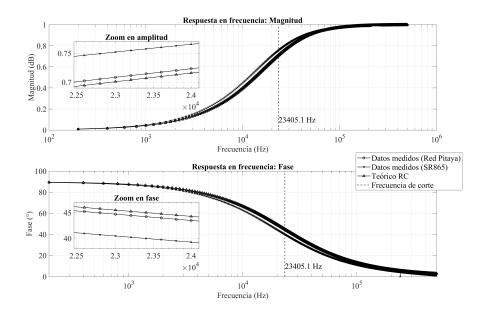

|          |                |                                | 4.3.3.4. Medición de transferencias conocidas                              | 92  |  |  |

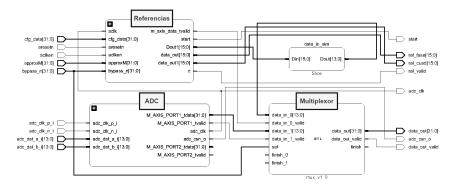

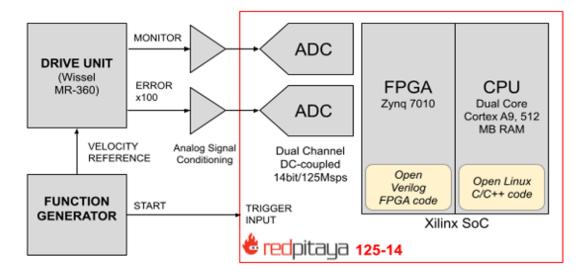

|          | 4.4.           | Impler                         | mentación del sistema en Red Pitaya                                        | 96  |  |  |

|          |                | 4.4.1.                         | Fuente de datos y conversor digital analógico                              | 97  |  |  |

|          |                | 4.4.2.                         | Lock-in                                                                    | 98  |  |  |

|          |                | 4.4.3.                         | Control del sistema                                                        | 99  |  |  |

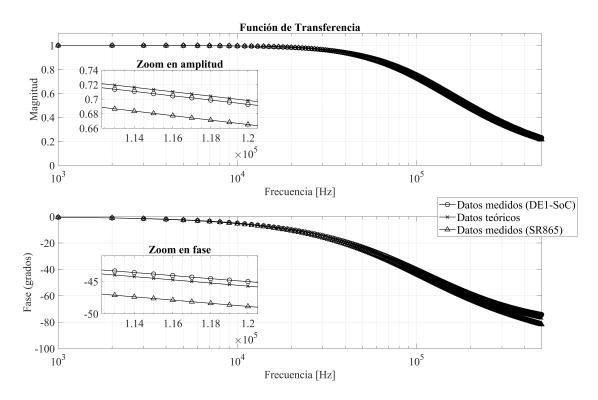

|          | 4.5.           | Result                         | ados en Red Pitaya                                                         | 99  |  |  |

|          |                | 4.5.1.                         | Uso de recursos y temporización                                            | 99  |  |  |

|          |                | 4.5.2.                         | Mediciones de ruido                                                        | 99  |  |  |

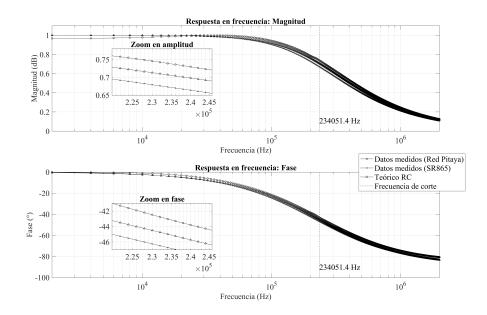

|          |                | 4.5.3.                         | Medición de transferencias conocidas                                       | 100 |  |  |

|          | 4.6.           | Compa                          | aración de DE-li y RP-li                                                   | 103 |  |  |

|          |                | 4.6.1.                         | Aspectos generales                                                         | 103 |  |  |

|          |                | 4.6.2.                         | Mediciones en f=100 kHz                                                    | 105 |  |  |

|          | 4.7.           | Conclu                         | usiones                                                                    | 107 |  |  |

|          |                |                                |                                                                            |     |  |  |

| <b>5</b> | $\mathbf{Apl}$ | icacion                        |                                                                            | 108 |  |  |

|          | 5.1.           | _                              | grafía de permeabilidad magnética                                          |     |  |  |

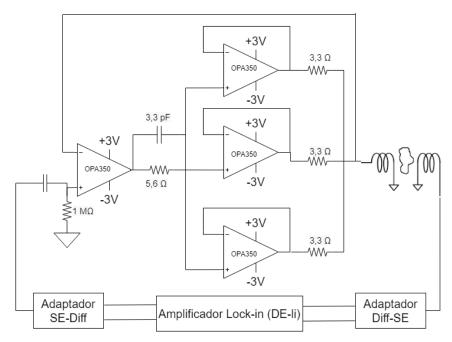

|          |                | 5.1.1.                         | Diseño del Tomógrafo Magnético                                             |     |  |  |

|          |                |                                | 5.1.1.1. Diseño del arreglo de bobinas y del circuito magnético            |     |  |  |

|          |                |                                | 5.1.1.2. Circuito controlador de campo magnético                           |     |  |  |

|          |                |                                | 5.1.1.3. Tiempos de medición                                               |     |  |  |

|          |                |                                | 5.1.1.4. Adaptación del DE-li al tomógrafo magnético                       |     |  |  |

|          |                |                                | 5.1.1.5. Reconstrucción                                                    | 113 |  |  |

|          |                | 5.1.2.                         | Resultados                                                                 |     |  |  |

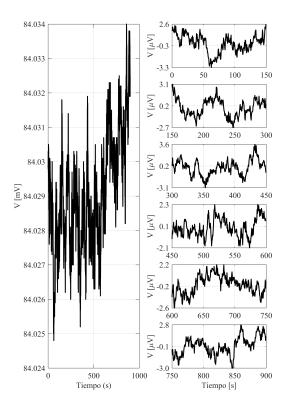

|          |                |                                | 5.1.2.1. Determinación del nivel de error en la medida de cada espira      |     |  |  |

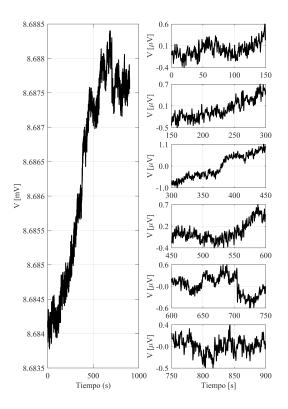

|          |                |                                | 5.1.2.2. Variaciones de $V_0$ en el tiempo                                 | 115 |  |  |

|          |                |                                | 5.1.2.3. Caracterización de las variaciones de tensión en espiras sensoras | 115 |  |  |

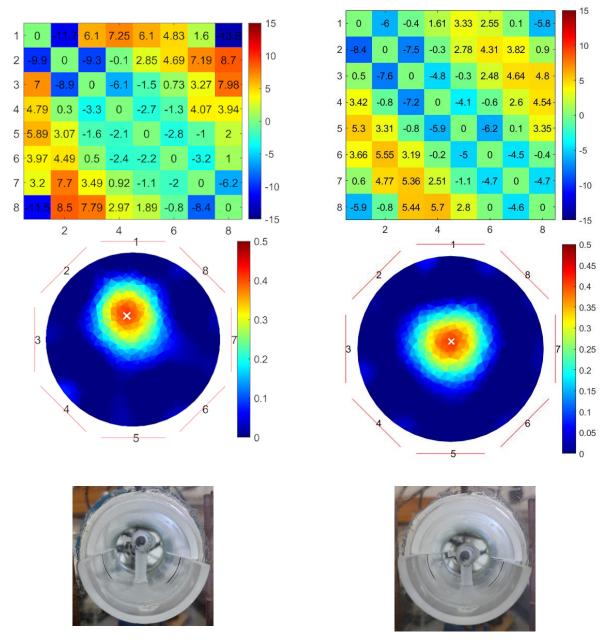

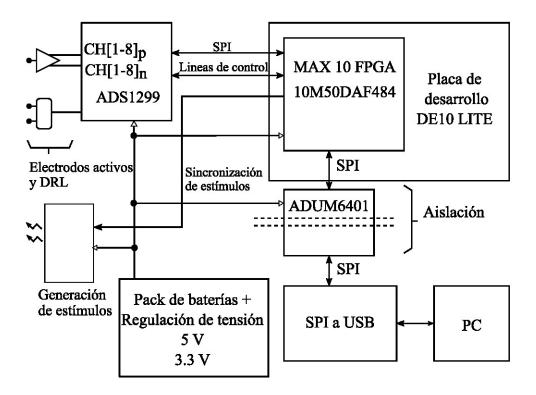

|          |                |                                | 5.1.2.4. Reconstrucción de imágenes con <i>phantoms</i>                    | 117 |  |  |

|          |                | 5.1.3.                         | Conclusiones                                                               | 117 |  |  |

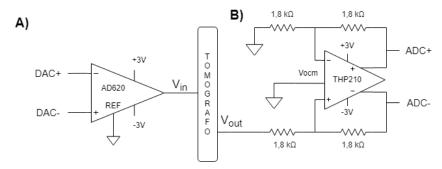

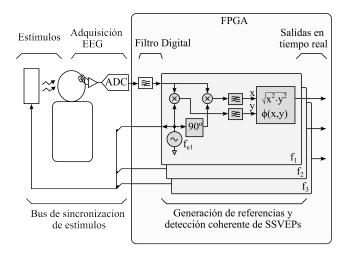

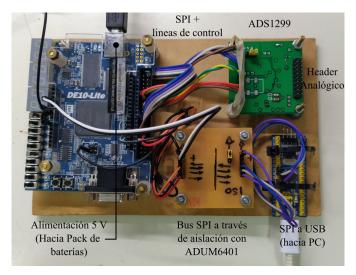

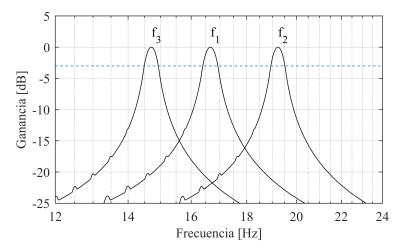

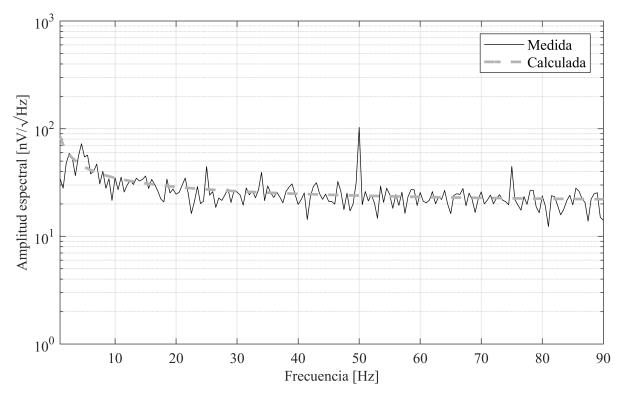

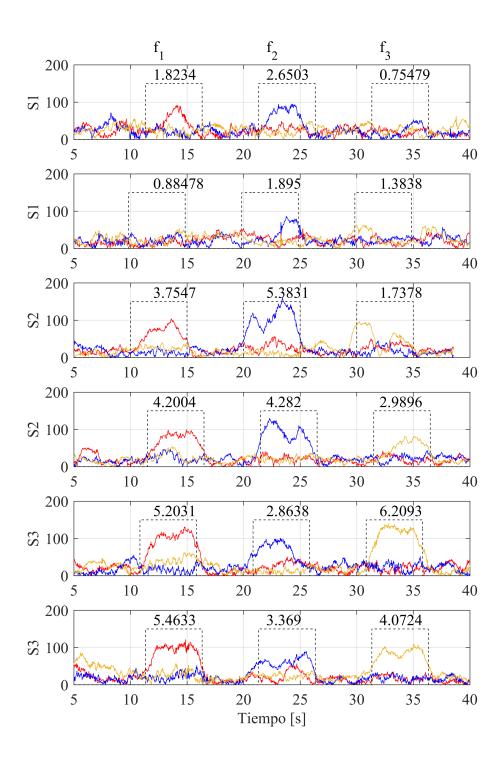

|          | 5.2.           | Interfaces cerebro computadora |                                                                            |     |  |  |

|          |                | 5.2.1.                         | Introducción                                                               | 121 |  |  |

|          |                | 5.2.2.                         | Implementación del sistema                                                 | 122 |  |  |

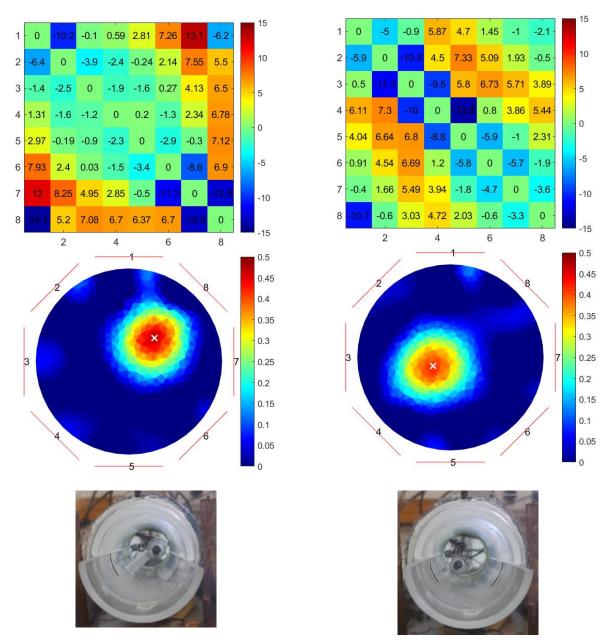

|          |                | 5.2.3.                         | Adquisición                                                                | 123 |  |  |

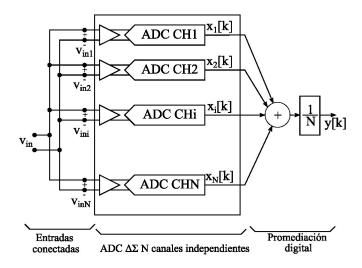

|          |                |                                | 5.2.3.1. Promediado de canales                                             | 124 |  |  |

|          |                |                                | 5.2.3.2. Interferencia electromagnética                                    | 126 |  |  |

|          |                | 5.2.4.                         | Alimentación y aislación                                                   | 126 |  |  |

|          |                | 5.2.5.                         | ·                                                                          |     |  |  |

|          |                | 5.2.6.                         | Estimulación visual                                                        | 128 |  |  |

|          |                | 5.2.7.                         | Resultados                                                                 |     |  |  |

|          |                |                                | 5.2.7.1. Medidas de ruido de adquisición con ADS131E08                     |     |  |  |

|          |                |                                | 5.2.7.2. Implementación del sistema de detección de SSVEPs                 |     |  |  |

|          |                |                                | 5.2.7.3. Medidas de SSVEPs                                                 |     |  |  |

|          |                |                                |                                                                            |     |  |  |

6 ÍNDICE GENERAL

|                               |                  | 5.2.8.  | Conclusio  | ones                                        | . 132 |

|-------------------------------|------------------|---------|------------|---------------------------------------------|-------|

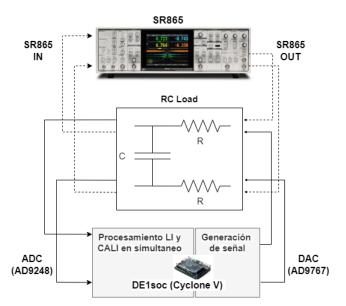

| 5.3. Espectroscopía Mössbauer |                  |         |            | Mössbauer                                   | . 135 |

|                               |                  | 5.3.1.  | Introduce  | ción                                        | . 135 |

|                               |                  | 5.3.2.  | Implemen   | ntación del sistema                         | . 137 |

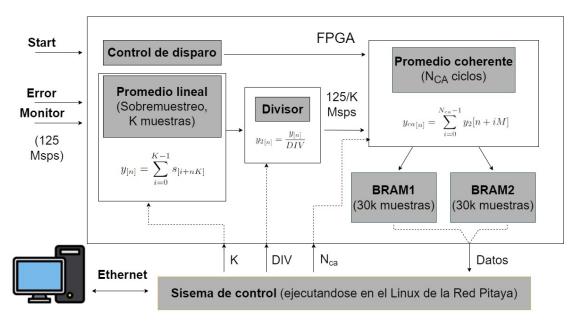

|                               |                  |         | 5.3.2.1.   | Procesamiento en la FPGA                    | . 138 |

|                               |                  |         |            | Promedio Lineal                             |       |

|                               |                  |         |            | Promediación Coherente                      |       |

|                               |                  |         | 5.3.2.4.   | Límites de $K$ y $N_{ca}$                   | . 140 |

|                               |                  |         |            | Control de Disparo                          |       |

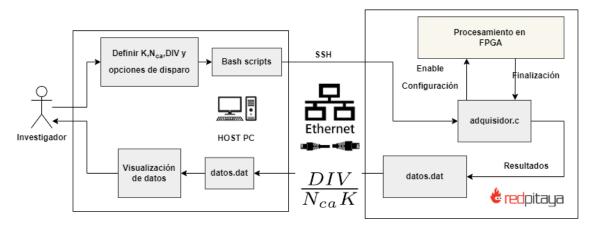

|                               |                  |         |            | Control del $\mu$ P                         |       |

|                               |                  | 5.3.3.  |            | OS                                          |       |

|                               |                  |         |            | Utilización de recursos                     |       |

|                               |                  |         |            | Validación del sistema                      |       |

|                               |                  | 5.3.4.  |            | ones                                        |       |

| 6                             | Con              | clusior | es, apor   | tes originales y líneas abiertas de trabajo | 144   |

|                               | 6.1.             | Conclu  | siones ger | nerales                                     | . 144 |

|                               | 6.2.             | Líneas  | abiertas c | le investigación                            | . 146 |

| Bi                            | Bibliografía 148 |         |            |                                             |       |

# Capítulo 1

# Introducción

#### 1.1. Sistemas de detección coherente

La medición de señales de amplitudes pequeñas inmersas en ruido es un problema común en instrumentación electrónica. Cuando se hacen mediciones de estas características, la relación entre la magnitud de la señal deseada y el nivel de ruido que la contamina suele conocerse como relación señal a ruido, y es usualmente representada por la sigla SNR, de su acrónimo en inglés.

A medida que decrece la SNR de un sistema es cada vez más difícil detectar la señal deseada. Sin embargo, si su frecuencia de oscilación es conocida o al menos estimable, o si puede modularse a una frecuencia conocida, es posible aplicar técnicas de detección (o demodulación) coherente para facilitar la tarea. Estas técnicas aprovechan el conocimiento de la frecuencia de la señal para procesarla, discriminando los datos de interés de la señal del ruido de fondo.

El interés por estas técnicas se remonta a 1941 [1], y en sus inicios se recurrió a circuitos puramente analógicos para detectar las señales de interés. A medida que la industria de electrónica digital fue avanzando, estas técnicas pasaron a aplicarse en sistemas muestreados con implementaciones digitales. Actualmente, existen dispositivos comerciales que realizan detección coherente de señales con enfoques mayormente digitales [2], [3]. Estos sistemas resultan muy útiles en aplicaciones de laboratorio, pero son instrumentos costosos y difíciles de incorporar en sistemas funcionales.

Para aplicar estas técnicas correctamente es clave mantener en todo momento el sincronismo de la señal medida con alguna señal de referencia interna, para aprovechar la periodicidad de la señal incógnita. Este requerimiento hace que la implementación de estos sistemas tenga estrictos requerimientos de tiempo real, lo que es difícil de cumplir con microprocesadores tradicionales, sobre todo cuando la frecuencia de la señal es elevada [4]. Es por esto que la mayoría de los dispositivos comerciales incorporan el procesamiento digital de la señal en lógica programable.

La implementación de estas técnicas de detección coherente en sistemas embebidos basados en lógica programable, con un enfoque de software y hardware abierto, y su aplicación a distintos escenarios es lo que ha motivado esta tesis.

### 1.2. Dispositivos SoC-FPGA

Un aspecto importante a considerar a la hora de implementar sistemas de detección coherente confiables es la plataforma en la que se implementarán estos sistemas, sobre todo cuando se quieren alcanzar frecuencias de demodulación altas, como en algunas de las aplicaciones que se han desarrollado durante esta tesis.

Existen variedad de plataformas que pueden servir a este propósito. La primera en que se puede pensar es en una computadora personal (PC). Las PCs son sistemas versátiles y potentes, capaces de ejecutar una amplia gama de aplicaciones y tareas. Pero su principal desventaja surge precisamente de que con ella se ejecutan muchos sistemas secuenciales en simultáneo. Un sistema de procesamiento y detección coherente de señales tiene importantes restricciones de tiempo real duro: aquellos en donde si el tiempo de respuesta está por encima de una cota se dice que ha fallado [4]. Estos requerimientos justifican la elección de sistemas embebidos (SE) para la aplicación de estas técnicas.

A diferencia de una PC convencional, un SE se caracteriza por un enfoque especializado y mayor eficiencia en recursos. Se denomina sistema embebido o empotrado a un sistema electrónico con capacidad de cómputo diseñado para ejecutar una o varias tareas bien específicas. En general los SE poseen menos capacidad de cómputo que las computadoras personales y se diseñan optimizando el tamaño y el consumo de energía [4].

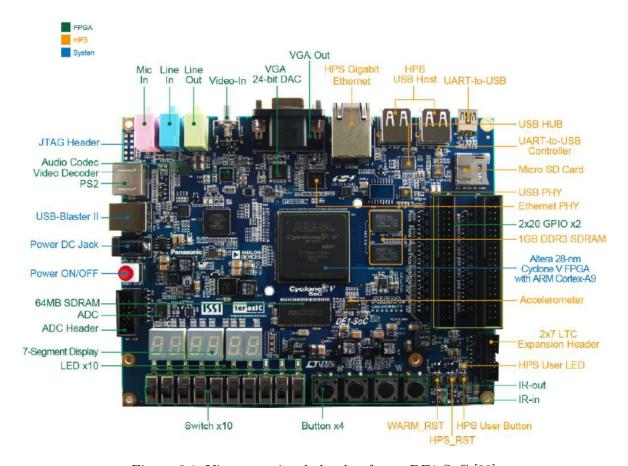

Una opción interesante para el desarrollo de SEs son los dispositivos SoC-FPGA, que se caracterizan por contar en un mismo chip con un microprocesador ( $\mu$ P) y un arreglo de celdas lógicas programables (FPGA de su acrónimo en inglés). La FPGA permite implementar directamente en hardware las tareas que requieren alta velocidad y determinismo, mientras que el microcontrolador le otorga flexibilidad al conjunto, permitiendo que se adapte a distintas condiciones, inclusive en tiempo de ejecución. El acrónimo SoC viene de system on chip: sistema en un chip.

La principal desventaja de estos sistemas tiene que ver con el tiempo de desarrollo. Un diseñador de sistemas SoC-FPGA enfrenta una curva de aprendizaje empinada y debe adquirir una variedad de habilidades para abordar con éxito los desafíos inherentes. Estos incluyen el diseño del hardware de la FPGA, en algún lenguaje de descripción de hardware como Verilog o VHDL, el desarrollo del software embebido que debe ejecutarse en el microprocesador y la comunicación exitosa de ambos elementos de procesamiento. Todo este proceso requiere de un diseñador especializado en diseño digital y en la arquitectura particular de la plataforma objetivo.

A lo largo de esta investigación se ha trabajado en simplificar este flujo de trabajo. En este sentido, se han desarrollado diseños modelo para el procesamiento de señales en SoC-FPGA, inicialmente en plataformas Intel-Altera y posteriormente adaptados con éxito a dispositivos de AMD-Xilinx. Luego, estos modelos fueron utilizados para implementar los sistemas de detección coherente, objeto de este trabajo, en dispositivos de ambos fabricantes. Todo el código generado es de acceso abierto y está disponible a través de los enlaces proporcionados en cada sección.

Si bien hay una enorme cantidad de contextos en los que se pueden aplicar las técnicas de procesamiento coherente de señales, la principal aplicación que ha impulsado este trabajo de investigación ha sido la implementación de un Tomógrafo Magnético, destinado a la detección de partículas ferromagnéticas en técnicas de terapias oncológicas. Mientras se perseguía este objetivo han surgido nuevas líneas de investigación, dando mayor valor al eje principal de este trabajo. En este sentido se destacan principalmente dos contribuciones adicionales: la implementación de sistemas de detección coherente en SoC-FPGA para impulsar interfaces cerebro computadora (comúnmente conocidas por sus siglas en inglés BCI, brain-computer interface) y la calibración de un equipo de Espectroscopía Mössbauer.

### 1.3. Técnicas tomográficas para detección de nanopartículas

#### 1.3.1. Hipertermia Magnética

Las propiedades curativas del calor en diversas enfermedades son conocidas desde hace mucho tiempo. Estas terapias, comúnmente conocidas como hipertermias, tienen sus primeros antecedentes hace unos 150 años, cuando Busch descubrió que los tumores dejan de crecer a temperaturas superiores a 42 °C, mientras que el tejido sano no se ve afectado [5]. Estas terapias han evolucionado enormemente a través de los años y actualmente dañar el tejido tumoral mediante un aumento local de la temperatura constituye una terapia contra el cáncer aprobada y establecida [6], [7]. Para lograr alcanzar las temperaturas necesarias para el tratamiento del cáncer en tejidos biológicos se han probado diversas técnicas [8], entre las cuales se pueden citar el calentamiento óhmico mediante corrientes de alta frecuencia aplicadas a través de electrodos [9], la irradiación por microondas aplicada a través de antenas de radiofrecuencia [10], [11], la irradiación láser a través de fibras [12] o el calentamiento en baño de agua [13]. Todas estas técnicas adolecen de un problema común: el control de la extensión espacial del calentamiento del tejido sigue siendo un desafío sin resolver [14].

La hipertermia por partículas magnéticas (o simplemente hipertermia magnética) busca resolver este problema introduciendo nanopartículas magnéticas (NPs), que actúan como fuente de calor, en el tejido tumoral. Las NPs se calientan mediante el uso de un campo magnético alternante externo, logrando controlar la extensión espacial del calentamiento del tejido. Los trabajos experimentales sobre hipertermia magnética se remontan hace casi 60 años [15] y en la actualidad han demostrado su éxito en los primeros ensayos clínicos [16], [17], [18], [19], en particular en tratamientos para el cáncer de próstata y gliomas. Estos ensayos además han mostrado que las molestias y efectos secundarios resultan moderados.

Si bien los estudios recientes de esta terapia son muy prometedores, el método aún necesita importantes mejoras antes de convertirse en un procedimiento médico estándar [20]. Para ello existen principalmente dos inconvenientes: por un lado, es crucial mejorar la potencia de calentamiento específica de las NPs para alcanzar y mantener temperaturas terapéuticamente adecuadas dentro del tejido tumoral con la menor cantidad posible de material magnético entregado al tumor. Por otro, es necesario determinar un método seguro, cómodo y reproducible para posicionar las NPs en la región tumoral.

Este es un problema particularmente desafiante, ya que el entorno biológico interactúa con las NPs, remodela su estructura y cambia sus propiedades. Esta interacción puede resultar en la eliminación de las NPs del cuerpo, o simplemente en una modificación en su distribución [21], [22]. En este contexto surge la necesidad de contar con una forma de determinar la posición en tiempo real de las NPs de una forma no invasiva, no destructiva, y sin contacto, para rastrear la distribución de las NPs antes y después del procedimiento médico [23].

La implementación de un instrumento diseñado para abordar este problema, considerando su importancia en el contexto de esta terapia oncológica emergente, es el principal problema que ha buscado solucionar este trabajo de investigación. Para aquellos lectores interesados en profundizar en las técnicas específicas, los ensayos clínicos y los antecedentes en hipertermia magnética, un resumen completo se encuentra disponible en [14].

#### 1.3.2. Tomografía Magnética

#### 1.3.2.1. Fundamentos

Para determinar en tiempo real la ubicación de las nanopartículas magnéticas las técnicas tomográficas resultan de especial interés. La tomografía es una técnica de exploración, que permite obtener imágenes de un corte o plano concreto de un cuerpo o un objeto [24]. Existen una amplia variedad de técnicas de tomografía, pero las técnicas eléctricas, en particular, cobran especial relevancia para el objeto de esta tesis. Si bien estas técnicas no ofrecen la mejor resolución de imagen, presentan características ventajosas para esta aplicación: son económicas, seguras, no invasivas y no utilizan radiación ionizante. Las técnicas eléctricas se pueden subdividir aún más y se ha prestado considerable atención a los métodos basados en la medición de cantidades eléctricas pasivas, a saber, resistencia (impedancia), capacitancia e inductancia [25].

La tomografía de impedancia eléctrica (EIT, por sus siglas en inglés) se basa en la medición de patrones de resistencia y reactancia [26], [27], [28] y puede producir imágenes de conductividad y permitividad. La tomografía de capacitancia eléctrica (ECT, por sus siglas en inglés) implica la medición de perfiles de capacitancia [29], [30], [31] y genera imágenes de distribuciones de permitividad. La tomografía de mutua inductancia, también conocida como tomografía de inductancia magnética (MIT, por sus siglas en inglés), completa el conjunto de estas técnicas, y es la que se desarrollará durante esta tesis.

Esta técnica tomográfica permite mapear, sin contacto y en forma no invasiva, las propiedades electromagnéticas pasivas (PEP) de un objeto mediante la medición de la inductancia mutua entre pares de bobinas colocadas alrededor de un perímetro [32], [33]. La MIT es sensible a las tres propiedades PEP de un objeto: conductividad eléctrica, permitividad dieléctrica y susceptibilidad magnética ( $\sigma$ ,  $\epsilon$  y  $\chi_m$  respectivamente). Esta última es una constante de proporcionalidad adimensional que indica el grado de sensibilidad a la magnetización de un material influenciada por un campo magnético externo. Se ha observado que existe una diferencia de varios ordenes de magnitud entre la  $\chi_m$  de los tejidos biológicos y la  $\chi_m$  de las NPs en coloides terapéuticos. En ausencia de NPs, los tejidos biológicos tienen una  $\chi_m$  del orden de  $10^{-6}$  [34], mientras que se espera que la susceptibilidad de una dosis terapéutica de NPs de óxido de hierro esté en el rango de  $10^{-4}$  a  $10^{-3}$  [35]. Esto implica que, si se pudiera ajustar la selectividad de MIT para la susceptibilidad magnética, podría emplearse esta técnica para detectar con éxito la presencia de NPs.

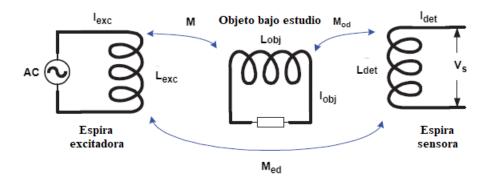

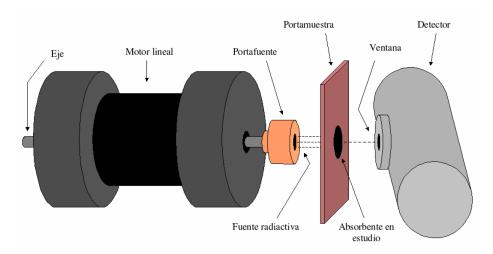

La Figura 1.1 muestra el esquema básico de un sistema de tomografía de mutua inductancia. Para su implementación es necesaria una espira excitadora y una espira sensora. Cuando una corriente eléctrica alterna circula a través de la espira excitadora se produce un campo eléctrico variable en ella. Este producirá un campo magnético en el espacio, que a su vez induce una tensión en la espira sensora. La naturaleza de esta tensión depende de las propiedades electromagnéticas del objeto ubicado entre las espiras, o de su ausencia. En consecuencia, esta medición permite inferir características relevantes del objeto.

Aumentando la cantidad de espiras se puede mejorar la resolución espacial del sistema. En un esquema de N espiras por ejemplo, cada espira puede ser utilizada alternativamente como excitadora o sensora, produciendo N-1 mediciones por espira, para un total de N(N-1) mediciones. Luego estas pueden utilizarse para reconstruir el medio circundante entre espiras y determinar la presencia o ausencia de NPs en él. Un buen resumen que cubre los avances de la metodología, la instrumentación y las aplicaciones de esta técnica se puede encontrar en [36].

Figura 1.1: Tomografía magnética. La figura muestra las inductancias de las distintas espiras y del objeto de interés, junto con las corrientes inyectadas o inducidas. También se representan la inductancia mutua entre la espira excitadora y el objeto bajo estudio (M), entre el objeto y la espira sensora  $(M_{\rm od})$  y entre espiras  $(M_{\rm ed})$ .

#### 1.3.2.2. Determinación de los parámetros de operación

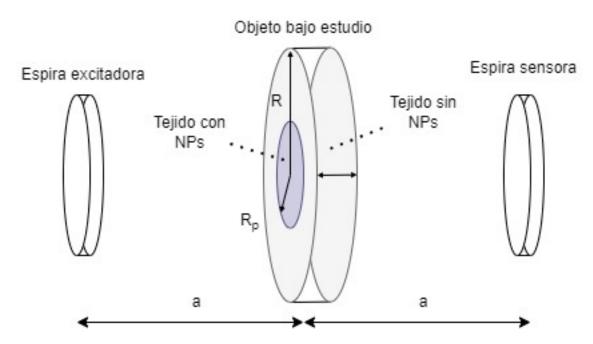

La determinación de las variaciones de tensión esperadas en la espira sensora es un problema complejo, que parte de las ecuaciones de Maxwell con condiciones de contorno adecuadas. Una solución analítica de estas ecuaciones diferenciales solo es posible en algunos casos simples. Por ejemplo, en [37] se propone una solución analítica para el caso de un objeto cilíndrico de radio R y grosor t posicionado coaxialmente a la mitad entre dos bobinas a una distancia 2a, con t  $\ll$  2a. Esta deducción puede extenderse para el caso que se muestra esquemáticamente en la Figura 1.2: un disco de tejido de radio R, grosor t y susceptibilidad despreciable, que incluye un disco más pequeño en su interior de radio  $R_p$  que contiene NPs con susceptibilidad magnética  $\chi_m$  [23].

En estas condiciones, considerando que la contribución magnética se debe exclusivamente a la susceptibilidad magnética de las NPs y simbolizando la conductividad eléctrica, la permeabilidad relativa del tejido y la frecuencia de operación con  $\sigma$ ,  $\epsilon_r$  y f respectivamente, se pueden expresar las variaciones de tensión en las bobinas de detección como:

$$\frac{\Delta B}{B} = \frac{\Delta V}{V} = K_p \chi_m + K \epsilon_r \epsilon_0 \omega^2 + K \sigma \omega, \qquad (1.1)$$

donde B es el campo magnético,  $\omega$  la frecuencia angular ( $\omega=2\pi f$ ) y  $\epsilon_0=8,85\times 10^{-12}\frac{\mathrm{F}}{\mathrm{m}}$  es la permitividad del vacío. K y K<sub>p</sub> dependen de la geometría y están dadas por:

$$K_{p} = a^{3} \frac{t}{2} R_{p}^{2} \frac{8a^{2} - R_{p}^{2}}{(a^{2} + R_{p}^{2})^{4}}$$

(1.2)

$$K = \mu_0 a^3 t \left( \frac{1}{a^2} - \frac{a^2 + 2R^2}{(a^2 + R^2)^2} \right)$$

(1.3)

donde  $\mu_0 = 4\pi 10^{-7} \frac{\text{H}}{\text{m}}$  representa la permeabilidad magnética del vacío.

La tensión inducida en la espira sensora para esta geometría en particular depende de tres términos: Uno proporcional a la susceptibilidad magnética,  $\chi_m$ , uno proporcional a la permitividad dieléctrica,  $\epsilon_r$ , y uno proporcional a la conductividad eléctrica,  $\sigma$ . Es importante notar que el término de interés, en el caso que nos concierne, es el que depende de  $\chi_m$ , que es el único que no

Figura 1.2: Modelo simplificado para una solución analítica de la tensión inducida en la espira sensora. Disco de radio R, que incluye una zona concéntrica de radio  $R_p$  que contiene NPs. El disco está centrado en el medio de dos espiras separadas 2a. El grosor del disco t es mucho menor a a.

depende de la frecuencia. Esto significa que se puede buscar una frecuencia de operación que haga despreciables los términos que dependen de  $\epsilon_r$  y  $\sigma$ , posibilitando la medición.

Examinando la ecuación 1.1 se ve que mientras más baja sea la frecuencia menor sera el aporte de los términos que dependen de  $\epsilon_r$  y  $\sigma$ , es decir que en un principio una frecuencia baja sería deseable para el experimento. Sin embargo, según la ley de Faraday, la tensión inducida en las espiras es proporcional a la variación temporal del campo magnético, por lo que éste resulta más difícil de detectar a medida que disminuye la frecuencia. En [23] se estudian los aportes de cada término en la ecuación 1.1 para distintos tejidos del cuerpo humano, como la sangre, el hígado, la grasa, el riñón, el pulmón y el intestino. En este análisis se llega a la conclusión de que una frecuencia de 100 kHz constituye una buena solución de compromiso entre una frecuencia de operación lo suficientemente alta para efectuar la medición, y una lo suficientemente baja para despreciar los términos no deseados, y es la frecuencia objetivo que se tomará a lo largo de este trabajo.

#### 1.3.2.3. Medición de la tensión en la espira sensora

Suponiendo que los términos no deseados son despreciables a la frecuencia de interés, y considerando una geometría como la descripta en la sección anterior, con  $2a=45\,\mathrm{mm},~R=40\,\mathrm{mm},$   $R_p=7\,\mathrm{mm}$  y  $t=1\,\mathrm{mm},$  las variaciones de tensión en la espira sensora que se pretender detectar pueden obtenerse a partir de las ecuaciones 1.1 y 1.2:

$$\frac{\Delta B}{B} = \frac{\Delta V}{V} \approx K_p \chi_m \approx 0.01174 \chi_m \tag{1.4}$$

Como se ha mencionado en la sección 1.3.2.1, la  $\chi_m$  de las NPs está en el rango de  $10^{-4}$  a  $10^{-3}$ . Suponiendo el peor caso para la detección, esto implica que se quiere medir una variación de tensión relativa de aproximadamente  $0,0117 \times 10^{-4} = 1,17 \times 10^{-6}$ .

Una medición de estas características no es sencilla, ya que la señal esta inmersa en ruido que puede ser de algunos ordenes de magnitud mayor. Sin embargo, la señal de excitación del experimento, es decir, la señal que pasa a través de la espira excitadora, es conocida, y de hecho es generada por el mismo aparato de medición. Esto posibilita utilizar sistemas de detección coherente de señal para realizar las mediciones.

### 1.4. Interfaces cerebro computadora

Las interfaces cerebro computadora (o BCIs, por su acrónimo en inglés) son dispositivos que proporcionan al usuario un nuevo canal de comunicación y control, para el cuál no debe realizar acciones motoras [38]. Para lograr este objetivo existen variedad de técnicas y métodos que están actualmente en desarrollo. En particular, el diseño de BCIs a partir de potenciales evocados visuales de estado estable (o SSVEPs por su acrónimo en inglés) es una técnica que ha demostrado ser efectiva para desarrollar dispositivos intuitivos, fáciles de usar y con altas tasas de transmisión de la información [39], [40].

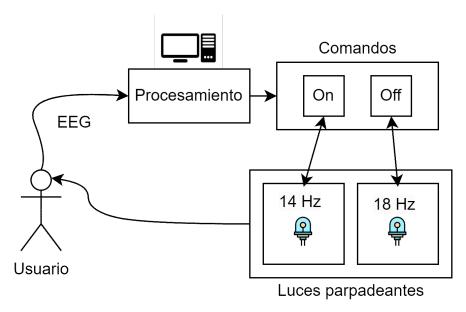

Estas técnicas se basan en un fenómeno que aparece en el registro electroencefalográfico (EEG) cuando una persona observa estímulos visuales periódicos con frecuencias superiores a 6 Hz. En estas condiciones, es posible detectar en el EEG una señal con la misma periodicidad que el estímulo visual. Asociando distintos comandos a distintas señales lumínicas, donde cada una parpadea a distintas frecuencias o en distintas fases, se puede generar un sistema que solo se valga del enfoque visual del usuario para controlar algún dispositivo. En la Figura 1.3 se muestra esquemáticamente un ejemplo de aplicación de esta técnica en un sistema simple con dos luces parpadeantes y dos comandos.

Esta aplicación tiene características ideales para la implementación de la técnica de detección coherente, ya que la señal evocada en el registro EEG es modulada por el mismo sistema, mediante

Figura 1.3: Ejemplo esquemático de una implementación de BCI basada en SSVEPs. El usuario puede mirar a dos luces parpadeantes, de 14 o 18 Hz. Según la periodicidad que se detecte en su registro EEG se activa un comando on/off.

estimulación lumínica en la frecuencia que se pretende detectar y, una vez medida, debe someterse a un procesamiento coherente, que detecte la presencia o ausencia de componentes en la frecuencia objetivo. En esta aplicación, la frecuencia de excitación y detección no es particularmente alta, sino en el orden de los Hz, pero es deseable que el sistema pueda realizar la detección coherente de señales en varias frecuencias simultáneamente, lo que se conoce como detección coherente multifrecuencial. Además, es deseable que la adquisición de la señal y la estimulación visual estén perfectamente sincronizadas, para facilitar la detección de los SSVEPs [41].

### 1.5. Espectroscopía Mössbauer

La Espectroscopía Mössbauer, también conocida como absorción resonante de rayos gamma, es una técnica que utiliza la emisión y absorción de fotones en núcleos de átomos determinados para estudiar características de los materiales. En esta técnica el núcleo de un átomo, en su estado excitado o radioactivo emite un fotón, que en ciertas circunstancias será absorbido por el núcleo de un átomo del mismo tipo, en estado absorbente o fundamental. Esta absorción, llamada absorción resonante, puede ser destruida si se cambia ligeramente la velocidad relativa entre los núcleos de los átomos. Aprovechando este fenómeno, la velocidad del núcleo excitado se varía en intervalos discretos y se analizan las mediciones del detector para cada velocidad. Al estudiar las velocidades en las que se produce la absorción resonante, es posible determinar características de los materiales.

Para que de esta operación surja un espectro de calidad adecuada es fundamental conocer la relación canal a velocidad del sistema de medida. Tradicionalmente, esta relación se obtiene a partir de un enfoque empírico, buscando que un espectro conocido tenga una relación canal a velocidad correcta [42],[43]. Sin embargo, las desviaciones de esta relación de la esperada son casi imposibles de predecir, y varían considerablemente cuando se modifican los parámetros de la velocidad o el sistema de control de lazo cerrado.

La velocidad de la fuente radiactiva suele ser controlada por un servo amplificador, del cual se distinguen dos señales de control: la señal Monitor, que es proporcional a la velocidad requerida en una bobina secundaria y la señal de Error, que es proporcional a la diferencia entre la tensión real en la bobina secundaria y la tensión requerida. Si se pueden medir estas señales en tiempo real, manteniendo el sincronismo y la resolución necesarias dadas por la aplicación, se puede determinar la relación canal a velocidad en tiempo real, mejorando los espectros obtenidos.

Las señales de Error y Monitor son periódicas, de frecuencias bajas (en el orden de 20 Hz), y para medirlas con la resolución deseada es conveniente contar con capacidades de promediación coherente. En un trabajo reciente [44], se realizó el muestreo de las formas de onda Error y Monitor con un osciloscopio digital estándar, manteniendo la sincronización y resolución necesarias para un análisis posterior. Aunque los osciloscopios tienen capacidades de promediación coherente, útiles para la adquisición de estas señales, los requisitos de este experimento exceden sus capacidades habituales, por lo que este procedimiento, que ha demostrado su utilidad, resulta una tarea laboriosa y temporalmente demandante.

Es en este punto donde encuentran utilidad los sistemas de detección coherente de señales. En esta aplicación, sin embargo, no es tan importante la velocidad a la que se muestrean las señales, sino su resolución. Además, este sistema debe poder recuperar, al menos, todo un periodo de la señal objetivo, en lugar de simplemente extraer la magnitud de esta señal del ruido circundante. Como este es un sistema con aplicaciones en laboratorios de Espectroscopía Mössbauer es deseable que el sistema sea versátil y fácilmente manipulable por investigadores no especializados en instrumentación electrónica. Si bien la elección de un sistema SoC-FPGA puede parecer sobre di-

mensionada para esta aplicación en particular, la incorporación de una herramienta de este tipo abre muchas áreas de trabajo a futuro en esta técnica.

# 1.6. Propuesta para un sistema de detección coherente en SoC-FPGA

Con estas aplicaciones en mente, y buscando aprovechar las características de los dispositivos SoC-FPGA, se decidió avanzar en la implementación de un sistema de detección coherente de señales reconfigurable, con capacidades para ser integrado en los distintos proyectos de interés.

Las características de las aplicaciones deseadas determinan algunas de las características del sistema a implementar. Este debe poder demodular señales de frecuencias desde unos pocos Hz hasta frecuencias en el orden de los cientos de kHz, para poder detectar la presencia de nanopartículas ferromagnéticas. También debe poder operar en múltiples frecuencias simultáneamente, para poder implementar con él un sistema de BCI de múltiples comandos, y debe poder recuperar periodos enteros de la señal con resoluciones adecuadas, para poder estudiar las señales de Error y Monitor del servoamplificador utilizado en la técnica de Espectroscopía Mössbauer. Además es deseable que el sistema sea fácil de utilizar, que sus parámetros de operación sean configurables en tiempo real y que la implementación sea flexible, de manera tal de poder adaptarla a distintos dispositivos de lógica programable y a las distintas aplicaciones.

### 1.7. Resumen de publicaciones producidas

Durante el desarrollo de este trabajo de tesis han surgido publicaciones en revistas y congresos, así como repositorios de hardware y software libre. Estos serán referenciados oportunamente a lo largo del texto y se presentan a continuación como resumen.

#### 1.7.1. Trabajos publicados en revistas

- [1] Matías J. Oliva et al. «Improving the computational efficiency of lock-in algorithms through coherent averaging». En: *Digital Signal Processing* 154 (2024), pág. 104693. ISSN: 1051-2004. DOI: https://doi.org/10.1016/j.dsp.2024.104693.

- [2] Matías Javier Oliva, Gustavo Pasquevich y Alejandro Luis Veiga. «Embedded device for digitalizing monitor and error signals in Mössbauer Spectroscopy». En: *Hyperfine Interact* 244.23 (2023). DOI: 10.1007/s10751-023-01834-5.

- [3] Matías Oliva et al. «Real-Time SSVEP Measurements Through Lock-In Detection in FPGA-Based Platform». En: Advances in Bioengineering and Clinical Engineering. Ed. por Fernando Emilio Ballina et al. Cham: Springer Nature Switzerland, 2024, págs. 161-171. ISBN: 978-3-031-61960-1. DOI: 10.1007/978-3-031-61960-1\_16.

- [4] M. J. Oliva et al. «SoC-FPGA systems for the acquisition and processing of electroencephalographic signals». En: *International Journal of Reconfigurable and Embedded Systems* (*IJRES*) 10.3 (nov. de 2021), págs. 237-248. DOI: 10.11591/ijres.v10.i3.pp237-248.

- [5] M. J. Oliva, P. A. García y E. M. Spinelli. «A System on Chip based electroencephalogram acquisition system». En: Revista Argentina de Bioingeniería 24.3 (2020). Presentado en Congreso Argentino de Bioingeniería 2020.

#### 1.7.2. Trabajos publicados en congresos

- [1] Matías Javier Oliva et al. «Open-source SoC-FPGA Platform for Signal Processing». En: Southern Programmable Logic Conference 2023. San Luis, Argentina, mar. de 2023.

- [2] Federico N. Guerrero, Matías Javier Oliva y Enrique Mario Spinelli. «Real-time noise reduction through independent channel averaging for real-time biomedical signal acquisition». En: Southern Programmable Logic Conference 2023. San Luis, Argentina, mar. de 2023.

- [3] Matías Javier Oliva et al. «Implementation of a digital Lock-in amplifier in SoC-FPGA for Biomedical Tomography». En: Congreso Argentino de Bioingeniería 2022. San Juan, Argentina, sep. de 2022.

- [4] P. A. García et al. «Bioimpedanciómetro basado en microcontrolador de 32 bits». En: Congreso Argentino de Bioingeniería 2022. San Juan, Argentina, sep. de 2022.

- [5] P. García, E. Spinelli y M. Oliva. «System on Chip based brain-computer interface». En: Congreso Argentino de Control Automático 2020. Buenos Aires, Argentina, oct. de 2020.

- [6] M. J. Oliva et al. «Interfaz cerebro computadora basada en SoC». En: Congreso Argentino de Sistemas Embebidos 2020. Buenos Aires, Argentina, ago. de 2020.

- [7] M. Haberman et al. «A wearable low-power and low-cost electromyographic sensor for arm prosthesis». En: Congreso Argentino de Bioingeniería 2020. Piriapolis, Uruguay, mar. de 2020.

- [8] Matías Javier Oliva, Pablo Andrés García y A. L. Veiga. «Evaluación del desempeño de sistemas embebidos heterogéneos para aplicaciones de tomografía magnética». En: *Jornadas de Investigación y Transferencia UNLP*. La Plata, Argentina, mar. de 2019.

- [9] M. J. Oliva et al. «Holter digital electrocardiográfico». En: Simposio Argentino de Sistemas Embebidos (SASE). Córdoba, Argentina, ago. de 2018.

#### 1.7.3. Repositorios de código abierto

- [1] Matías Oliva. Repositorio con recursos para probar el algoritmo CALI. https://github.com/ushikawa93/lockin\_coherent\_average. 2023.

- [2] Matias Oliva. Signal processing in FPGA. https://github.com/ushikawa93/signal\_processing\_fpga.git. 2022.

- [3] Matías Oliva. Signal Processing Red Pitaya. https://github.com/ushikawa93/signal\_processing\_red\_pitaya. 2024.

- [4] Matías Oliva. Funcionalidades para controlar un lockin SR865 de Stanford en forma remota. https://github.com/ushikawa93/sr865\_software. 2024.

- [5] Matías Oliva. Lock-in en DE1-SoC. https://github.com/ushikawa93/lockin\_de1soc. 2024.

- [6] Matías Oliva. Lock-in en Red Pitaya. https://github.com/ushikawa93/lockin\_redpitaya. 2024.

- [7] Matías Javier Oliva. SSVEP FPGA ADS1299. https://github.com/ushikawa93/ssvep\_fpga\_ads1299. 2024.

- [8] M.J. Oliva. Adquisidor en Red Pitaya. https://github.com/ushikawa93/adquisidor\_ red\_pitaya. 2024.

#### 1.8. Estructura de la tesis

En este capítulo han presentado las principales motivaciones y objetivos de este trabajo de investigación. En el capítulo 2 se describen en detalle los sistemas de detección coherente de señales, incluyendo resultados teóricos conocidos y originales. En el capítulo 3 se describen los dispositivos SoC-FPGA, y las plataformas de procesamiento de señales que se han desarrollado para éstos durante esta tesis, mientras que en el capítulo 4 se describe la implementación de sistemas de detección coherente en SoC-FPGA, comparando los resultados obtenidos con la bibliografía disponible, y con sistemas comerciales similares. El capítulo 5 muestra las aplicaciones de los sistemas desarrollados. Este se divide en tres partes: el desarrollo del tomógrafo magnético, la implementación de una interfaz cerebro computadora basada en potenciales evocados visuales y la incorporación de los sistemas desarrollados a la calibración de un sistema de Espectroscopía Mössbauer. Finalmente, en el capítulo 6 se discuten los resultados obtenidos, se plantean conclusiones y se delinea el trabajo que se pretende desarrollar a futuro.

# Capítulo 2

# Técnicas de detección coherente

#### 2.1. Introducción

Medir señales de amplitudes pequeñas perturbadas por ruido es un desafío típico en instrumentación electrónica, que aparece en áreas tan diversas como las telecomunicaciones, la bioingeniería o el control automático. Un parámetro esencial para la descripción de este tipo de sistemas es la relación señal a ruido (SNR), que cuantifica la amplitud de la señal de interés frente al ruido en la que está inmersa. En sistemas en donde se conoce la amplitud o la potencia de la señal y del ruido esta magnitud puede calcularse mediante las fórmulas 2.1 y 2.2.

$$SNR_{dB} = 20 \log_{10} \left( \frac{A_{se\tilde{n}al}}{A_{ruido}} \right)$$

(2.1)

$$SNR_{dB} = 20 \log_{10} \left( \frac{A_{se\tilde{n}al}}{A_{ruido}} \right)$$

$$SNR_{dB} = 10 \log_{10} \left( \frac{P_{se\tilde{n}al}}{P_{ruido}} \right)$$

(2.1)

Cuanto menor sea esta magnitud, es decir, cuanto más ruido haya en el sistema, más complicado será detectar la señal deseada. Sin embargo, si se conoce o al menos se puede estimar la frecuencia de oscilación de la señal desconocida, o si esta se puede modular a una frecuencia conocida, pueden aplicarse técnicas de procesamiento coherente para posibilitar la tarea. Entre éstas existen aquellas que aplican algoritmos que no realimentan la señal de salida, comúnmente llamadas técnicas de lazo abierto, y aquellas que utilizan los datos de salida para realimentar y robustecer los cálculos, conocidas como técnicas de lazo cerrado [45].

Las técnicas de lazo cerrado utilizan algoritmos recursivos para minimizar el error entre la información modelada y la medida, con el objetivo de estimar una variable desconocida. Existen distintos algoritmos para optimizar este proceso, entre los cuales se pueden mencionar el filtro de Kalman [46], [47], [48], el filtro de Lyapunov[49], [50], [51] y las técnicas de diseño directo [52].

Entre las técnicas de lazo abierto se encuentran el Lock-in y la promediación coherente, que son de las más estudiadas en la bibliografía disponible. El estudio y desarrollo de estas técnicas es el que ha impulsado este trabajo de investigación, y en el que se centra esta tesis. En este capítulo se presentan en detalle, incluyendo antecedentes, resultados conocidos y originales.

Gran parte de los resultados que se muestran en este capítulo fueron presentados en [53] y [54].

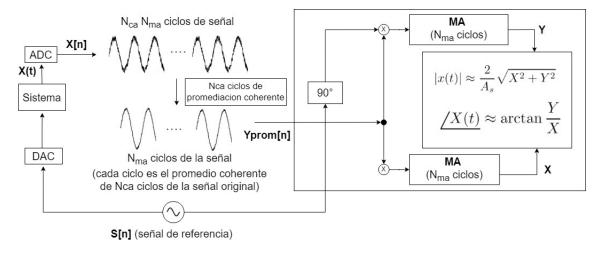

#### 2.2. Lock-in

El amplificador Lock-in es una herramienta muy utilizada en instrumentación científica. Su implementación permite obtener información de señales de banda estrecha moduladas a una frecuencia determinada,  $f_c$ . Para ello se utiliza una señal periódica de referencia, que puede ser cuadrada o sinusoidal, de la misma frecuencia, y opcionalmente una señal de referencia desfasada 90°. Este último paso divide a esta técnica en Lock-in de una fase (o canales) y de dos fases.

#### 2.2.1. Lock-in de una fase

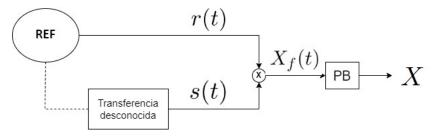

La Figura 2.1 muestra la forma más elemental de aplicar el concepto de *Lock-in*. Se dispone de una señal de referencia r(t), que oscila a la frecuencia  $f_c$ , y una señal desconocida s(t), que puede ser la modulación de una señal desconocida a la frecuencia  $f_c$  o la respuesta de un sistema cuando es excitado por una señal de esta frecuencia.

$$r(t) = A_r \operatorname{sen}(\omega_c t + \phi_r)$$

$$s(t) = A_s \operatorname{sen}(\omega_c t + \phi_s)$$

donde  $\omega_c = 2\pi f_c$ . La señal s(t) se multiplica por la referencia, obteniendo la señal  $X_f(t)$ , que puede expresarse como:

$$X_f(t) = \frac{A_s A_r}{2} \cdot (\cos(\phi_r - \phi_s) - \cos(2\omega_c t + \phi_r + \phi_s))$$

(2.3)

y consta de dos términos: un término de continua y uno que oscila al doble de la frecuencia  $f_c$ . Esta señal ingresa a un filtro pasa-bajos que, suponiendo que puede rechazar totalmente el término de frecuencia  $2f_c$ , proporciona un salida dada por:

$$X = \frac{A_s A_r}{2} \cdot \cos(\phi_r - \phi_s) \tag{2.4}$$

Este resultado depende de la diferencia entre la fase de la señal de referencia y la señal desconocida, y alcanza su máximo valor cuando ambas fases coinciden. Como la referencia es una señal accesible para el usuario se puede ajustar su fase hasta encontrar el máximo en la señal X,  $X_{max}$ , para finalmente obtener la amplitud de la señal desconocida como:

$$A_s = 2 \cdot \frac{X_{max}}{A_r} \tag{2.5}$$

Si bien este método permite recuperar correctamente la amplitud de la señal desconocida, su aplicación implica ajustar manualmente la fase de la referencia, dificultando la medición, e incorporando una fuente de error adicional. Estos problemas pueden solucionarse utilizando una señal de referencia extra, desfasada 90° de la original, como se verá en la próxima sección.

#### 2.2.2. Lock-in de dos fases

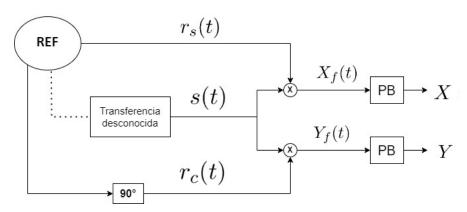

Al agregar al sistema una señal de referencia desfasada 90° se puede eliminar la dependencia de los resultados con el desfasaje de las señales. Considerando las señales indicadas en la Figura 2.2 se pueden distinguir:

$$r_s(t) = A_r \operatorname{sen}(\omega_c t + \phi_r)$$

$$r_c(t) = A_r \operatorname{cos}(\omega_c t + \phi_r)$$

$$s(t) = A_s \operatorname{sen}(\omega_c t + \phi_s)$$

Figura 2.1: Lock-in de una fase

La señal desconocida es multiplicada por la señal de referencia (comúnmente llamada referencia en fase), y por la señal desfasada 90° (conocida como referencia en cuadratura), para luego aplicar sendos filtros pasa-bajos a las señales obtenidas, en un procedimiento análogo al descripto para el *Lock-in* de una fase.

$$X_f(t) = \frac{A_s A_r}{2} \cdot (\cos(\phi_r - \phi_s) - \cos(2\omega_c t + \phi_r + \phi_s))$$

$$Y_f(t) = \frac{A_s A_r}{2} \cdot (\sin(\phi_r - \phi_s) - \sin(2\omega_c t + \phi_r + \phi_s))$$

$$X = \frac{A_s A_r}{2} \cdot \cos(\phi_r - \phi_s)$$

$$Y = \frac{A_s A_r}{2} \cdot \sin(\phi_r - \phi_s)$$

(2.6)

De donde se pueden despejar tanto la amplitud como la fase de la señal desconocida:

$$A_s = \frac{2}{A_s} \sqrt{X^2 + Y^2} \tag{2.8}$$

$$\phi_s = \frac{2}{A_r} \arctan\left(\frac{Y}{X}\right) \tag{2.9}$$

Con este sencillo procedimiento es posible eliminar la necesidad de ajustar manualmente la fase de la referencia, evitando una posible causa de errores, y contribuyendo a la automatización del proceso, a cambio de duplicar los recursos, ya sea digitales o analógicos, necesarios para la implementación del *Lock-in*.

Figura 2.2: Lock-in de dos fases

#### 2.2.3. Análisis en el Dominio Complejo

Las deducciones dadas en las secciones 2.2.1 y 2.2.2 pueden presentarse en forma más compacta considerando señales en el plano complejo. Para ello se tomará una referencia compleja dada por:

$$r(t) = A_r e^{j(\omega_c t + \phi_r)}$$

=  $A_r \cos(\omega_c t + \phi_r) + j A_r \sin(\omega_c t + \phi_r)$

Por simplicidad se considerará una señal de entrada cosenoidal, que puede representarse en notación compleja como:

$$s(t) = A_s \cos(\omega_c t + \phi_s)$$

$$= \frac{A_s}{2} (e^{j(\omega_c t + \phi_s)} + e^{-j(\omega_c t + \phi_s)})$$

Ahora esta señal se multiplica por la referencia compleja, obteniendo:

$$s(t)r(t) = \frac{A_s A_r}{2} (e^{j(\omega_c t + \phi_s)} + e^{-j(\omega_c t + \phi_s)}) e^{j(\omega_c t + \phi_r)}$$

$$= \frac{A_s A_r}{2} (e^{j2\omega_c t} e^{j(\phi_r + \phi_s)} + e^{j(\phi_r - \phi_s)})$$

Y es luego sometida a un pasa-bajos, eliminando el término del doble de frecuencia, obteniendo:

$$P_{B}\{s(t)r(t)\} = \frac{A_{s}A_{r}}{2}e^{j(\phi_{r}-\phi_{s})}$$

$$= \frac{A_{s}A_{r}}{2}(\cos(\phi_{r}-\phi_{s})+j\sin(\phi_{r}-\phi_{s}))$$

(2.10)

donde se ha simbolizado la operación de pasa-bajos con el operador  $P_B\{\}$ . Tomando la parte real y la parte imaginaria de esta última ecuación se llega a las mismas expresiones de X e Y dadas en la sección anterior:

$$Re\{P_B\{s(t)r(t)\}\} = X = \frac{A_s A_r}{2} \cdot \cos(\phi_r - \phi_s)$$

$$Im\{P_B\{s(t)r(t)\}\} = Y = \frac{A_s A_r}{2} \cdot \sin(\phi_r - \phi_s)$$

de donde pueden deducirse las expresiones 2.8 y 2.9, que corresponden al módulo y la fase de la magnitud compleja dada por la ecuación 2.10.

Es interesante notar, además, que en la condición  $\phi_s = \phi_r$  la parte real de este resultado es máxima, igual a  $\frac{A_s A_r}{2}$  y la parte imaginaria de el resultado es igual a 0. Este es el caso que se busca ajustando la fase de la referencia hasta que el resultado sea máximo cuando se hace *Lock-in* de una fase, de donde se desprende que el *Lock-in* de una fase es un caso particular del *Lock-in* de dos fases.

#### 2.2.4. Efecto sobre el ruido blanco

Para abordar la pregunta de cómo este esquema de procesamiento de señales contribuye a reducir el ruido en la salida del sistema, es crucial delinear las características del ruido que lo afecta. En esta sección se considerará el efecto del ruido blanco n(t), definido como un proceso aleatorio

estacionario en sentido amplio (PAESA), con distribución gaussiana, media nula y varianza  $\sigma^2$ , es decir, un proceso cuyas muestras siguen una distribución  $\mathcal{N}(0,\sigma^2)$ . Además, se asumirá que las muestras del proceso en distintos momentos no están correlacionadas entre sí, por lo que su función de autocorrelación se puede modelar mediante la función generalizada conocida como delta de Dirac  $(\delta(\tau))$  y la desviación estándar del ruido  $(\sigma_i)$  según:

$$R_{nn}(\tau) = \sigma_i^2 \delta(\tau) \tag{2.11}$$

La densidad espectral de potencia de este proceso puede obtenerse tomando la transformada de Fourier de esta función de autocorrelación, como establece el teorema de Wiener-Khinchin [55], [56]:

$$S_{nn}(f) = \int_{-\infty}^{\infty} R_{nn}(\tau) e^{-j2\pi f \tau} d\tau$$

$$= \int_{-\infty}^{\infty} \sigma_i^2 \delta(\tau) e^{-j2\pi f \tau} d\tau = \sigma_i^2$$

con lo que se llega a una definición alternativa del ruido blanco: un proceso aleatorio con densidad espectral de potencia (DEP) constante para todas las frecuencias:

$$S_{nn}(f) = \sigma_i^2 = \frac{N_0}{2} \qquad \forall f$$

donde los términos  $\frac{N_0}{2}$  y  $\sigma_i^2$ , se utilizarán en forma equivalente a lo largo de este texto.

En este punto vale una aclaración: este tipo de proceso es en realidad una abstracción matemática, ya que la potencia media de una señal como esta sería infinita, por lo que no tiene sentido físico. Esto puede mostrarse integrando esta densidad espectral sobre todas las frecuencias:

$$\langle p \rangle = \int_{-\infty}^{\infty} S_{nn}(f)df = \int_{-\infty}^{\infty} \frac{N_0}{2} df \longrightarrow \infty$$

(2.12)

Sin embargo, esta abstracción permite introducir el concepto de ruido blanco limitado en banda, definido como un proceso cuya densidad espectral de potencia es constante e igual a  $\frac{N_0}{2}$  dentro de un cierto ancho de banda  $B_n$ , y nula fuera de él:

$$S_{nn}(f) = \begin{cases} \frac{N_0}{2} & |f| < B_n \\ 0 & \text{en otro caso} \end{cases}$$

(2.13)

Ahora sí, la potencia media de este proceso es finita:

$$\langle p \rangle = \int_{-\infty}^{\infty} S_{nn}(f) \, df = \int_{-B_n}^{B_n} \frac{N_0}{2} \, df = N_0 \cdot B_n$$

(2.14)

Se supondrá entonces que la señal original, s(t), está formada por la señal de interés  $s_0(t)$  y por ruido blanco limitado en banda n(t):

$$s(t) = s_0(t) + n(t) (2.15)$$

Esta es la señal que ingresa al Lock-in. En el análisis que sigue se considerará  $s_0(t) = 0$ , sin perder generalidad gracias al principio de superposición. Se considerará el caso de Lock-in de dos

fases ya que, como se ha visto en la sección 2.2.3, el *Lock-in* de una fase es un caso particular de éste.

La señal s(t) es multiplicada por una exponencial compleja  $(e^{j2\pi f_c t})$ , considerando 0 la fase de la referencia por simplicidad) y luego sometida a un pasa-bajos, para finalmente tomar el módulo del resultado (equivalente a la ecuación 2.8) y su fase (equivalente a la ecuación 2.9). Primero se considerará la multiplicación, que provoca un desplazamiento de las componentes del ruido en la frecuencia. Para analizar esto se planteará la función de autocorrelación de la señal multiplicada  $n_{mult}(t) = n(t)e^{j2\pi f_c t}$ . Como n(t) es un proceso PAESA esta autocorrelación está dada por:

$$R_{n_{mult}n_{mult}}(\tau) = E\{n_{mult}(t)n_{mult}^{*}(t+\tau)\}$$

$$= E\{n(t)e^{j2\pi f_{c}t}n^{*}(t+\tau)e^{-j2\pi f_{c}(t+\tau)}\}$$

$$= E\{n(t)n^{*}(t+\tau)e^{-j2\pi f_{c}\tau}\}$$

$$= R_{nn}(\tau)e^{-j2\pi f_{c}\tau}$$

(2.16)

donde el superíndice \* denota el conjugado de la magnitud compleja. Conociendo el par transformado  $R_{nn} \leftrightarrow S_{nn}(f)$ , y aplicando la propiedad de traslación de la transformada de Fourier:

$$f(t)e^{j2\pi\alpha t} \iff F(f-\alpha)$$

(2.17)

puede verse que la densidad espectral de potencia de la señal multiplicada  $n(t)e^{j2\pi f_c t}$  sigue siendo  $\frac{N_0}{2}$ , pero ahora centrada en  $f + f_c$ :

$$S_{mult}(f) = S_{nn}(f + f_c) = \begin{cases} \frac{N_0}{2} & -B_n < f + f_c < B_n \\ 0 & \text{En otro caso} \end{cases}$$

$$S_{mult}(f) = \begin{cases} \frac{N_0}{2} & -B_n - f_c < f < B_n - f_c \\ 0 & \text{En otro caso} \end{cases}$$

(2.18)

Es decir que el ruido que se encontraba en las inmediaciones de la frecuencia  $f_c$  termina en banda base, y será este el ruido que aparecerá en la salida del sistema luego del filtrado pasa-bajos. Con esto ya se puede ver que la acción conjunta de mezclador y filtro será equivalente a un pasa-banda centrado en la frecuencia de interés  $f_c$ .

Llegados a este punto es necesario delinear las propiedades del filtro pasa-bajos que se utilizará. Considerando a este filtro como lineal e invariante en el tiempo, con una función de transferencia H(f), la densidad espectral de potencia en su salida será:

$$S_o(f) = |H(f)|^2 S_{mult}(f)$$

(2.19)

Si además el filtro es ideal, es decir que su función de transferencia es un cajón de una cierta ganancia K de ancho  $\Delta f$ :

$$H(f) = \begin{cases} K & -\frac{\Delta f}{2} < f < \frac{\Delta f}{2} \\ 0 & \text{En otro caso} \end{cases}$$

(2.20)

se puede calcular la densidad espectral de ruido a la salida del Lock-in según:

$$S_o(f) = \begin{cases} K^2 \frac{N_0}{2} & -\frac{\Delta f}{2} < f < \frac{\Delta f}{2} \\ 0 & \text{En otro caso} \end{cases}$$

(2.21)

donde se supuso que el ancho de banda donde el ruido puede considerarse blanco incluye a la banda de paso del filtro.

A partir de este resultado se puede calcular la autocorrelación de ruido a la salida haciendo uso nuevamente del teorema de Wiener-Khinchin. Luego considerando que en el ruido blanco limitado en banda no hay correlación entre los valores de señal en dos momentos distintos, la potencia media se puede obtener evaluando esta autocorrelación en  $\tau = 0$ .

$$R_{xx}(\tau) = \int_{-\infty}^{\infty} S_o(f) e^{-j2\pi f \tau} df$$

$$= \int_{-\frac{\Delta f}{2}}^{\frac{\Delta f}{2}} K^2 \frac{N_0}{2} e^{-j2\pi f \tau} df = \frac{N_0}{2} K^2 \frac{e^{j2\pi \frac{\Delta f}{2}\tau} - e^{-j2\pi \frac{\Delta f}{2}\tau}}{j2\pi \tau}$$

$$= \frac{N_0}{2} K^2 \Delta f \frac{e^{j\pi \Delta f \tau} - e^{-j\pi \Delta f \tau}}{2j\pi \Delta f \tau} = \frac{N_0}{2} K^2 \Delta f \frac{f \operatorname{sen}(\pi \Delta f \tau)}{\pi \Delta f \tau}$$

$$(2.22)$$

Definiendo la función  $\operatorname{sinc}(x) = \frac{\operatorname{sen}(x)}{x}$ , que tiene la propiedad de aproximarse infinitamente a 1 cuando x = 0, se puede sintetizar este resultado y obtener la potencia media de ruido a la salida:

$$R_{xx}(\tau) = \frac{N_0}{2} K^2 \Delta f \quad \operatorname{sinc}(\Delta f \pi \tau)$$

$$R_{xx}(0) = K^2 \frac{N_0}{2} \Delta f = K^2 \frac{N_0}{2} \Delta f \tag{2.23}$$

Lo cual lleva al resultado:

$$\sqrt{\frac{R_{xx}(0)}{\frac{N_0}{2}}} = \frac{\sigma_o}{\sigma_i} = K\sqrt{\Delta f}$$

(2.24)

Si bien este es un análisis simplificado, permite discernir algunos aspectos de la acción del Lock-in. La desviación estándar del ruido en la salida disminuye proporcionalmente con la raíz cuadrada

del ancho de banda del filtro pasa-bajos utilizado, con lo cual la elección de éste resulta un factor

clave en su diseño. Con filtros más selectivos se obtiene una mayor reducción del ruido a la salida.

Idealmente si se pudiese lograr  $\Delta f = 0$  se rechazaría todo el ruido a la salida, aunque esto implicaría

integrar la señal durante un tiempo infinito.

#### 2.2.5. Elección del filtro pasa-bajos

Como muestra el análisis anterior, la combinación de multiplicación y filtro pasa-bajos se comporta como un pasa-banda centrado en  $\omega_c$ , sin muchas de las dificultades asociadas con el diseño de filtros pasa banda estrechos [57]. Esto implica que un elemento clave en la amplificación Lock-in es la selección del filtro pasa bajos [58]. Este cumple con dos propósitos: en primer lugar, debe eliminar la componente de frecuencia doble en la señal multiplicada. En segundo lugar, se encarga de reducir el ruido que se involucra en los cálculos.

#### 2.2.5.1. Filtro de media móvil

Una opción interesante para la técnica Lock-in es un filtro de media móvil simple (o MAF, del inglés moving average filter) de largo T. La operación de este filtro sobre una entrada continua arbitraria x(t) puede describirse matemáticamente mediante su respuesta impulsional, dada por 2.25.

$$h(t) = \begin{cases} \frac{1}{T} & -\frac{T}{2} < t < \frac{T}{2} \\ 0 & \text{En otro caso} \end{cases}$$

(2.25)

En el dominio frecuencial esta operación resulta:

$$H(\omega) = \int_{-\frac{T}{2}}^{\frac{T}{2}} \frac{1}{T} e^{-j\omega t} d\omega = \frac{1}{T} \frac{e^{-j\frac{T}{2}\omega} - e^{j\frac{T}{2}\omega}}{-j\omega} = \frac{\operatorname{sen}(\frac{\omega T}{2})}{\frac{\omega T}{2}} = \operatorname{sinc}\left(\frac{\omega T}{2}\right)$$

(2.26)

Los ceros de la función sinc se dan cuando su argumento es igual a  $m\pi$ , con  $m \neq 0$ :

$$\frac{\omega_m T}{2} = m\pi \to \omega_m = \frac{m2\pi}{T} \tag{2.27}$$

Es decir que siempre que  $f=m\frac{1}{T}$  la función presentará un cero. Si se elige T como un múltiplo entero del periodo de la función de referencia  $(T=k\frac{1}{f_c})$  resulta que los ceros caen en  $f=kmf_c\to f=\alpha f_c$ , es decir en múltiplos enteros de la frecuencia de interés  $f_c$ . Esto resulta especialmente interesante para la acción del Lock-in, que debe bloquear el componente del doble de frecuencia generado por el mezclador. En el caso del Lock-in con MAF este bloqueo será total, ya que el filtro presenta un cero en esta frecuencia.

Para este filtro, el ancho de banda es inversamente proporcional al largo T  $(\Delta f = \frac{\alpha}{T})$ . Esto implica que si se utiliza en la técnica *Lock-in*, el ruido de medición puede reducirse promediando un mayor número de periodos de la señal [59], [60]. Para un análisis más detallado de esto se examinará qué ocurre con el ruido luego de la acción conjunta del mezclador y el filtro MAF. Para ello se partirá de la ecuación 2.19 y se calculará la DEP de ruido a la salida para determinar la potencia de ruido:

$$S_{o}(f) = |H(f)|^{2} S_{mult}(f) = \frac{N_{0}}{2} \operatorname{sinc}^{2}\left(\frac{\omega T}{2}\right)$$

$$R_{nn}(\tau) = \frac{N_{0}}{2} F^{-1} \left\{\operatorname{sinc}^{2}\left(\frac{\omega T}{2}\right)\right\} = \frac{N_{0}}{2} \frac{2}{T} F^{-1} \left\{\operatorname{sinc}^{2}(\omega)\right\} = \frac{N_{0}}{2} \frac{2}{T} \operatorname{Tri}(\tau)$$

$$R_{nn}(0) = P_{o} = \frac{N_{0}}{2} \frac{2}{T}$$

(2.28)

Donde se ha tenido en cuenta el par transformado  $\operatorname{sinc}^2(\omega) \leftrightarrow \operatorname{Tri}(t)$ , con  $\operatorname{Tri}(x)$  representando la función triangular, dada por:

$$Tri(x) = \begin{cases} 1 - |x| & |x| \le 1\\ 0 & \text{En otro caso} \end{cases}$$

Ahora se puede relacionar el ruido en la entrada con el ruido a la salida del sistema:

$$\frac{\sigma_o^2}{\sigma_i^2} = \frac{\frac{N_0}{2} \frac{2}{T}}{\frac{N_0}{2}} \longrightarrow \sigma_o = \frac{\sigma_i}{\sqrt{\frac{T}{2}}}$$

$$(2.29)$$

Por lo que con MAF de largo T el *Lock-in* reduce la potencia de ruido en un factor  $\sqrt{\frac{T}{2}}$ .

Todo este análisis se ha hecho para señales analógicas. En sistemas digitales, muestreados a una frecuencia de muestreo  $f_m$  ( $T_m = \frac{1}{f_m}$ ), el filtro MAF de un número entero de ciclos de la señal puede describirse matemáticamente según:

$$Y_{[n]} = \frac{1}{NM} \sum_{k=n}^{n+NM-1} x_{[k]}$$

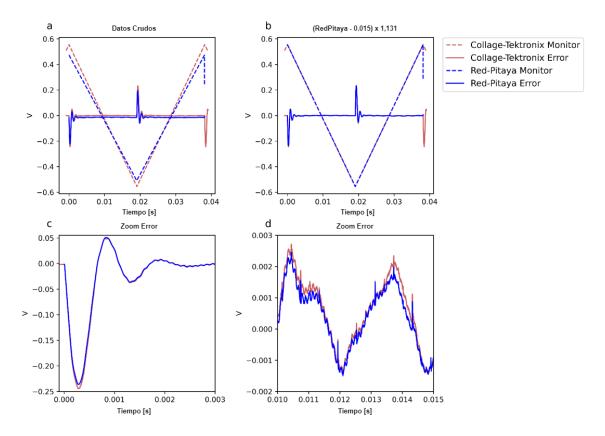

(2.30)