# Generación automática de circuitos paralelos de multiplicación para DSP a medida de la aplicación

Nelson Acosta & Cecilia Collado

INCA – Departamento de Computación y Sistemas – Facultad de Ciencias Exactas Universidad Nacional del Centro de la Provincia de Buenos Aires 7000 - Tandil – Argentina – TE: +54 - 2293 - 432466

> Email: nacosta@exa.unicen.edu.ar http://www.exa.unicen.edu.ar/inca/

**RESUMEN**: En éste artículo se presenta una herramienta para la generación automática de multiplicadores paralelos en VHDL para síntesis. Se intenta asistir al diseñador de DSP a medida sobre plataformas FIPSOC (de Sidsa) o Virtex (de Xilinx). Se generan los siete multiplicadores: McCanny - McWhirter, De Mori, Hatamian y Cash, Ripple Carry, Carry Save, Guild y De Mori - Guild; con y sin *pipelining*.

CLAVES: generación automática de circuitos, síntesis de circuitos, CAE, multiplicación.

## 1.-Introducción

Como contrapartida a la programación de aplicaciones sobre una computadora de uso general, mediante la adaptación del conjunto de instrucciones a la aplicación (programación de arquitectura de *Von Neumann*), se puede considerar el desarrollar una aplicación con un circuito digital totalmente a medida de la aplicación. Hace unos años eso era impensable para volúmenes pequeños o medianos, pero la FPGA ha producido una reducción de costos que hacen posible diseñar máquinas de cálculo totalmente a medida de la aplicación, aún para series muy pequeñas con costos bajos.

En el desarrollo de sistemas empotrados (*embedded*) y sistemas digitales de tratamiento de señales hay necesidad de módulos tales como: máquinas de estado, multiplicadores, divisores, cálculos trigonométricos, operaciones con matrices, microcontroladores, módulos de comunicación, interfaces para buses estándar, controladores de vídeo, etc.. Por otro lado, la disponibilidad de FPGAs de tamaños medianos (de más de 20.000 puertas) y grandes (de entre 200.000 y 1.000.000 de puertas) ha permitido aplicaciones con diseños basados en lenguajes de descripción de hardware (VHDL, Verilog, Hardware-C, Handel-C, Abel, etc.) con síntesis automática. Utilizando estas herramientas se ha extendido el desarrollo y comercialización de módulos IP (de Propiedad Intelectual), normalmente para microcontroladores, procesadores, DSP, entre otras aplicaciónes. Esta alternativa permite al diseñador comprar los diseños de productos de funcionamiento ya comprobado, que puedan ser incorporados al proyecto como un componente más. Para el desarrollo de aplicaciones hardware a medida de las aplicaciones normalmente se debe comprar un módulo IP con las características fijadas al momento de la compra y que son inamovibles (lo que no permite la actualización sin costo del producto).

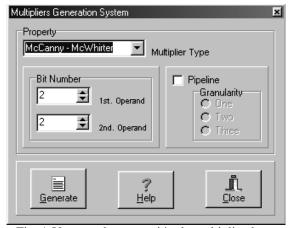

Fig. 1-Ventana de generación de multiplicadores

Los sistemas (académicos o comerciales) que generan multiplicadores normalmente se basan en sólo un tipo de multiplicador [Bue98], y además no contemplan la posibilidad de generar circuitos combinacionales y/o con diferentes grados de *pipelining*.

En éste artículo se presenta una herramienta para la generación automática de multiplicadores paralelos mediante la generación de VHDL para síntesis automática. Se presentan los siete multiplicadores (McCanny - McWhirter, De Mori, Hatamian y Cash, Ripple Carry, Carry Save, Guild y De Mori – Guild) generados por la herramienta, en versión combinacional o con *pipelining* de grado 1, 2 o 3. Además, cada una de estas versiones puede tener operandos con tamaño seleccionado por el usuario.

## 2.-Sistema de generación automática de multiplicadores

La multiplicación es siempre una función esencial en sistemas digitales, es parte vital de cualquier circuito de procesamiento digital de señales. El presente trabajo se centra en multiplicadores paralelos, orientados a la velocidad de procesamiento.

Para la materialización de los circuitos se utiliza VHDL por RTL<sup>1</sup>, así luego el usuario puede realizar la síntesis utilizando, por ejemplo el FPGA Express (de Synopsys provisto por el Xilinx Foundation Series) produciendo con el Foundation versión 1.4 una lista de conexiones en formato XNF.

La utilización del sistema es muy simple, se selecciona el tipo de multiplicador deseado (de acuerdo a ello), se selecciona el tamaño de los operandos (entre 2 y 16 bits). Si se desea que el multiplicador trabaje con *pipelining* se puede seleccionar una granularidad entre 1 y 3. Actualmente el sistema está siendo evaluado por dos empresas fabricantes de FPGAs para ser distribuido entre las aplicaciones de sus sistemas: Xilinx (www.xilinx.com) y Sidsa (www.sidsa.es). Una vez que el código VHDL ha sido generado, dicho módulo puede ser incorporado a cualquier diseño que permita la definición del sistema usando este lenguaje de descripción de hardware.

# 3.-Multiplicadores propuestos

A continuación se describen los siete multiplicadores organizados por forma de comunicación entre PE (procesadores elementales). Nótese que cada multiplicador calcula **A\*B+C+S**, generando un número resultado cuyo tamaño es la suma de los tamaños de **A** más el de **B**. En cada caso se destacan las características principales, del estado del arte presentado en [Aco00].

# 3.1.-De Comunicación Local

# 3.1.a) McCanny - McWhirter

Esta topología presenta comunicación local entre PE<sup>1</sup>; fue publicado por J. McCanny y J. McWhirter en 1982 [Mcc82].

#### 3.1.b) De Mori

Este multiplicador totalmente sistólico fue sugerido por R. de Mori [Mo69].

## 3.2-De Comunicación Global

# 3.2.a) Hatamian y Cash

En este circuito, cuya estructura es idéntica al multiplicador McCanny - McWhirter, la segmentación se realiza difundiendo uno de los operandos y pasando el otro de manera sistólica. Fue implementado por primera vez por Hatamian y Cash [Hat86, Boe97]. Los bits de un operando son pasados horizontalmente hacia la derecha, mientras que los bits del otro operando son pasados verticalmente hacia arriba [Bue98].

# 3.2.b) Ripple - Carry

Este circuito representa a un multiplicador combinacional cuyo PE se reduce a la combinación de una puerta AND y un *full adder* de un bit [Dav83]. Los dos bits de los operandos son pasados a otro PE vía las salidas **a** (en forma horizontal de derecha a izquierda) y **b** (en forma vertical hacia abajo) [Bue98].

## 3.2.c) Carry Save

Este circuito representa a un multiplicador combinacional cuyo PE se reduce a la combinación de una puerta AND y un *full adder* de un bit [Dav83, Obe79]. Los dos bits de los operandos son pasados a otro PE vía las salidas **a** (en forma horizontal de derecha a izquierda) y **b** (en forma diagonal izquierda hacia abajo). En la situación general donde **A**, **B**, **S** y **C** tienen **n** dígitos, después de los **n** pasos del proceso se obtienen dos enteros cuyas sumas es igual al valor numérico  $\mathbf{A} * \mathbf{B} + \mathbf{C} + \mathbf{S}$ . Estos dos enteros son sumados por una cascada de *full adders*. Las cadenas de PEs de las que se obtienen los bits del resultado  $\mathbf{P}_n$  hasta  $\mathbf{P}_{(n-1)}^2$ , finalizan con un sumador *half adder* o *full adder* según corresponda.

<sup>&</sup>lt;sup>1</sup> RTL Register Transfer Level

<sup>&</sup>lt;sup>1</sup> PE: Procesador elemental. Celda básica del multiplicador.

## 3.3-De Comunicación Mixta

## 3.3.a) Guild

Este circuito fue propuesto por H. H. Guild [Gui69]. Es un tipo de circuito caracterizado por un alto *throughput*, debido al uso de ambos, paralelismo y *pipelining*. Está compuesto por un *array* de **n**<sup>2</sup> PEs. Es un multiplicador semisistólico, esto es, que tiene una comunicación mixta (local-global) entre los PEs. De los circuitos analizados este multiplicador es uno de los más simples, interesantes y económicos.

# 3.3.b) De Mori - Guild

Este multiplicador es un híbrido entre los multiplicadores De Mori y Guild [Boe96]. La entrada de datos tiene una estructura similar a la del multiplicador Guild, lo cual permite difundir bits de uno de los operandos en un único ciclo de reloj. Esta topología puede ser estructurada considerando  $\mathbf{n}^2$  bits. Como consecuencia, la latencia es menor que la correspondiente al multiplicador De Mori. El operando  $\mathbf{a}$  presenta una comunicación mixta: el bit  $\mathbf{a}_0$  es totalmente global,  $\mathbf{a}_1$  es global para tres PEs y se transmite para el ultimo PE;  $\mathbf{a}_2$  es global para dos PEs y se transmite para los dos últimos PEs; y el bit  $\mathbf{a}_3$  se transmite de manera local en los cuatro PEs.

## 4.-Conclusión

Con respecto a las métricas de los multiplicadores generados se puede concluir que el Guild es el más económico, seguido por el Hatamian-Cash. En ese orden también son los más utilizados debido a su alto *throughput* (por el uso del paralelismo y *pipelining*).

El sistema de generación de multiplicadores forma parte del proyecto de desarrollo de módulos de propiedad intelectual del grupo INCA. Este módulo ha sido enviado para su evaluación para ser incorporado en el kit de herramientas de Xilinx y Sidsa. En este momento se está verificando desarrollos completos, en los cuales el multiplicador trabaja como coprocesador de un microcontrolador (8051 de intel en el FIPSOC de Sidsa, mientras que en 68hc08 y 8051 en el caso de la familia Virtex de Xilinx).

### Referencias

- [Aco00] N. Acosta, E. Todorovich, C. Collado & K. Larsen, "Multiplicadores paralelos: estado del arte y análisis de su implementación en FPGA"; V IBERCHIP, San Paulo (Brasil) 1994.

- [Ang94] J. M. Angulo & Deschamps Jean-P, "Diseño de sistemas digitales"; Paraninfo; 1994.

- [BJM93] E. I. Boemo, E. Juárez y J. Meneses; "*Taxonomía de Multiplicadores*"; VIII DCIS Conference, Universidad de Málaga, Noviembre de 1993.

- [Boe96] E. I. Boemo; "Contribution to the Design of Fine-Grain Pipelined Arrays"; https://www.ii.uam.es/~ivan/; January 1996.

- [Boe97] E. Boemo, G. Gonzalez de Rivera, S. López-Buedo y J. Meneses; "*Un Estudio sobre Circuitos Segmentados en FPGAs*"; Dpto. de Ingeniería Electrónica, ETSI Telecomunicación, Univerisdad Politécnica de Madrid; Madrid España 1997.

- [Bue98] S. López Buedo; "The Webgen Project"; http://www.ii.uam.es/~eda; 1998.

- [Col99] C. Collado & K. Larsen; "Sistema de Asistencia en el Diseño de Multiplicadores"; Tesis de Grado. UNCPBA, Fac. Ciencias Exactas, Depto. De Computación y Sistemas, Tandil, 1999.

- [Dav83] M. Davio, J. Deschamps, A. Thayse; "Digital System"; 1983.

- [Des95] J. Deschamps; "Descripción en VHDL y Simulación de Sistemas Digitales"; 1995.

- [Gui69] H. H. Guild. "Fully Iterative Fast Array for Binary Multiplication and Addition"; Electronic Letters, pp. 263, Vol. 5, Nro. 12; Junio 1969.

- [Hat86] Hatamian M. & Cash G. L. "A 70-Mhz 8-bit x 8 bit Parallel Pipelined Multiplier in 2.5-um CMOS"; IEEE Journal of Solid-State Circuits; August 1986.

- [McC82] McCanny J. V. & J. McWirter. "Completely iterative, pipelined multiplier array suitable for VLSI"; IEEE Proc. pp. 40-46, Vol. 129, Part. G, N<sup>ro.</sup> 2; Abril 1982.

- [Mo69] R. De Mori; "Suggestion for an I.C. Fast Parallel Multiplier"; Electronic Letters, Vol. 5, N<sup>ro.</sup> 3, pp. 50-51: Febrero 1969.

- [Obe79] R.M.M. Oberman. "Digital Circuits for Binary Arithmetic", 1979.