# PROCESAMIENTO PARALELO

# CÓMPUTO PARALELO EN UNA ARQUITECTURA HETEROGÉNEA

Año 2000

ALUMNOS: CARLOS OMAR RIVARES ADRIÁN EDUARDO EVANGELISTA

DIRECTOR: FERNANDO GUSTAVO TINETTI

TES 00/10 DIF-02114 SALA

A mis viejos y hermano, por el aliento y ser los pilares de mi vida; y también a mis amigos/as por ser la familia que supe elegir.

# **CARLOS OMAR RIVARES**

A toda mi familia: abuelos, padres, hermanos, hermanas, cuñada, y especialmente a mis sobrinos Juan Martín y María Victoria, que me dieron la fuerza necesaria para que esto sea posible.

ADRIAN EDUARDO EVANGELISTA

# **Agradecimientos**

Nuestro primer agradecimiento es a nuestro director por el apoyo, paciencia y empeño invertido en esta tesis. Al profesor Fernando Romero por habernos aguantado todos los días y todo el día en el laboratorio de paralelo y habernos enseñado a soldar "cablecitos" para el hipercubo. También agradecemos las infinitas veces que Alejandra Pizarro nos posibilitó la llave del laboratorio de paralelo como así también la recepción de la misma. No nos olvidamos tampoco de Andrés Barbieri que nos brindó sus amplios conocimientos en Linux en momentos de total incertidumbre. También por los conocimientos en procesamiento paralelo y especialmente en transputers a Laura De Guisti y Diego Tarrío.

También queremos agradecer a nuestras familias y amistades que nos apoyaron en los buenos y malos momentos y que gracias a ellos fue posible nuestra continuidad.

Por último, y no por eso menos importante, agradecemos al director del laboratorio LIDI, Ingeniero Armando De Giusti, y al laboratorio mismo por la posibilidad de utilizar las instalaciones a nuestro gusto y brindarnos las herramientas y bibliografía para el desarrollo de este trabajo.

# Indice

| 1. Introducción                                                  | l        |

|------------------------------------------------------------------|----------|

| 1.1. Procesamiento paralelo                                      | 2        |

| 1.2. Multiplicación de matrices                                  | 3        |

| 1.3. Definiciones generales                                      |          |

| 1.4. Arquitecturas de procesamiento                              | 6        |

| 1.5. Organización del informe                                    |          |

| 2. Redes de computadoras heterogéneas                            | 9        |

| 2.1. Introducción a PVM                                          | 10       |

| 2.2. Sistema PVM                                                 | 11       |

| 3. El transputer                                                 | 13       |

| 3.1. Características de un transputer                            | 13       |

| 3.2. Arquitectura de un transputer                               |          |

| 3.3. El procesador                                               |          |

| 3.4. Acceso a memoria                                            |          |

| 3.5. Los ports seriales de E/S                                   | 19       |

| 3.6. Aspectos técnicos del CSA Educational Kit                   |          |

| 4. Algoritmos de multiplicación de matrices                      | 22       |

| 4.1. Block cyclic data distribution                              |          |

| 4.2. Modelo de cálculo                                           | 23       |

| 4.3. SUMMA                                                       | 24       |

| 4.3.1. Esquema de comunicación de SUMMA                          | 26       |

| 4.3.2. Tiempo de espera innecesario de SUMMA                     | 26       |

| 4.4. DIMMA                                                       | 30       |

| 4.4.1. Esquema de comunicación de DIMMA                          | 30       |

| 4.4.2. Concepto de LCM                                           | 35       |

| 4.4.3. Pseudo-código de DIMMA                                    |          |

| 5. Diseño de multiplicación de matrices en transputers           |          |

| 5.1. Ruteo de mensajes                                           |          |

| 5.2. Procesos master y slave                                     |          |

| 6. Implementación de la multiplicación de matrices en transputer |          |

| 6.1. Implementación del router                                   |          |

| 6.1.1. Deadlocks                                                 |          |

| 6.1.2. Canales virtuales                                         |          |

| 6.1.3. Detalles de implementación del router                     |          |

| 6.2. Implementación DIMMA                                        |          |

| 6.2.1. Dimensiones de las matrices                               |          |

| 6.2.2. Tamaños de mensajes                                       |          |

| 6.2.3. Implementación Master/Slave                               |          |

| 7. Integración de la red de transputers con PVM                  |          |

| 7.1. Forma de integración                                        | 53       |

| 7.2. Procesos en el host                                         |          |

| 7.2.1. Comunicaciones entre procesos en el host y los transp     | outers55 |

| 7.2.2. Forma de integración ideal                                |          |

| 7.2.3. Mejora en la integración                              | 56 |

|--------------------------------------------------------------|----|

| 7.3. Algoritmo global                                        |    |

| 8. Resultados obtenidos y conclusión                         | 58 |

| 8.1. Parámetros de experimentación                           | 58 |

| 8.1.1. Dimensiones de las matrices                           | 58 |

| 8.1.2. Tamaño de los bloques                                 | 58 |

| 8.1.3. Tamaño de buffers                                     | 58 |

| 8.2. Resultados obtenidos                                    | 59 |

| 8.2.1. Tiempo en los transputers                             | 59 |

| 8.2.2. Tiempos totales                                       |    |

| 8.3. Conclusiones                                            |    |

| 8.4. Trabajo futuro                                          |    |

| A. I (C/ D 1.1                                               |    |

| A: Lenguaje 'C' Paralelo                                     |    |

| Proceso de compilación y linking                             |    |

| Carga y ejecución                                            |    |

| Primitivas para implementar concurrencia                     |    |

| Canales virtuales                                            |    |

| B: Librería de PVM                                           |    |

| Control de procesos                                          |    |

| Información                                                  |    |

| Configuración dinámica                                       |    |

| Configuración y consulta de opciones                         |    |

| Pasaje de mensajes                                           |    |

| Buffers de mensajes                                          |    |

| Empaquetamiento de datos                                     | 80 |

| Envío y recepción de datos                                   | 81 |

| Desempaquetamiento de datos                                  | 82 |

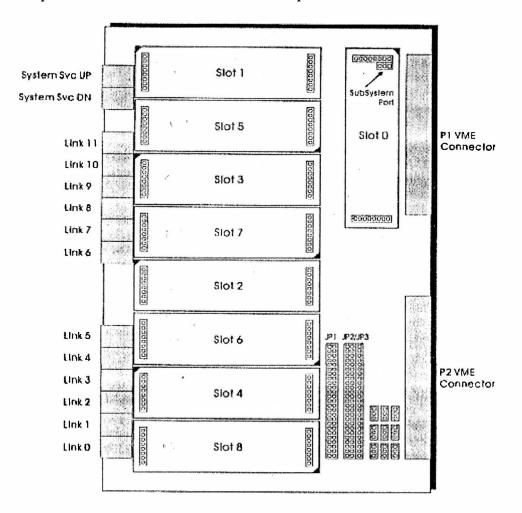

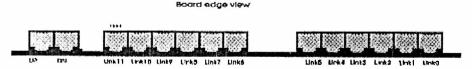

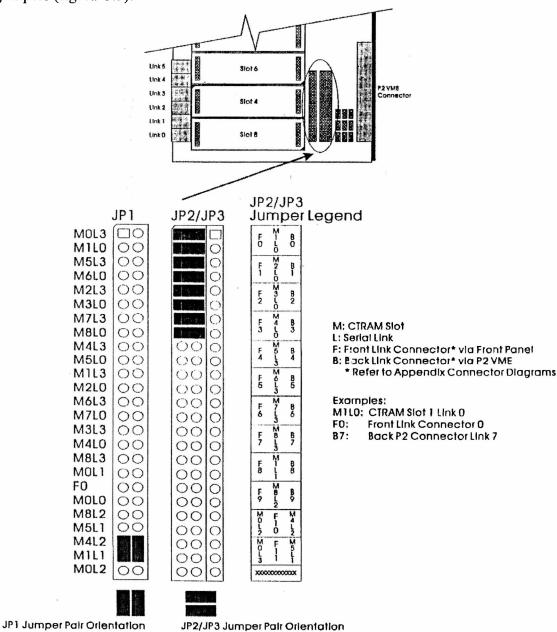

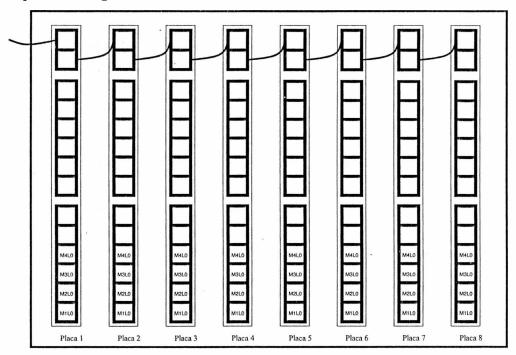

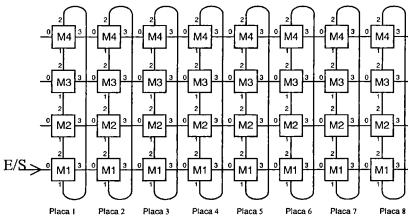

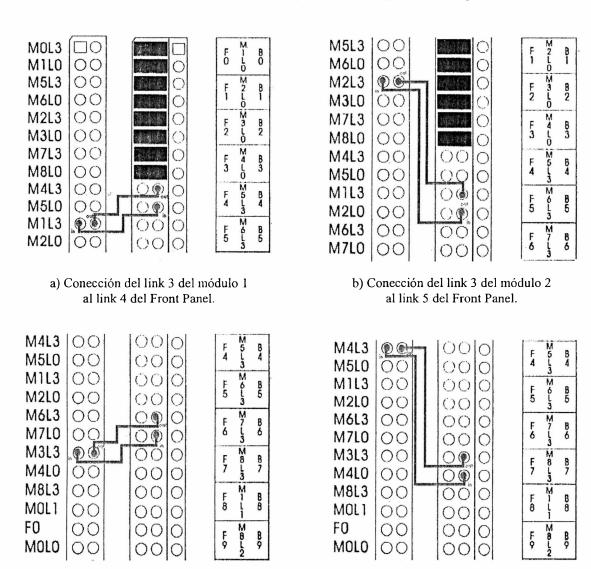

| C: Configuración del hipercubo como una grilla               | 84 |

| Jumpers de la placa VME-XP                                   |    |

| Link configuration Array                                     | 86 |

| Configuración anterior                                       | 87 |

| Nueva configuración                                          |    |

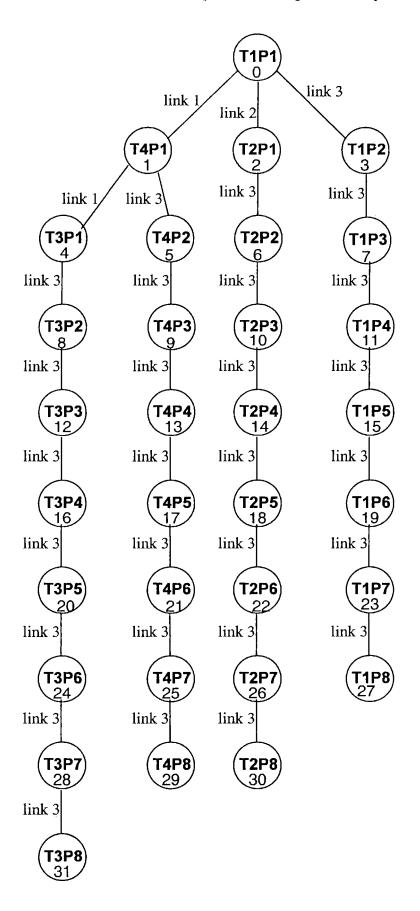

| Numeración de los transputers                                |    |

| D: PVM para windows 95/NT                                    |    |

| Nueva arquitectura                                           |    |

| Implementación                                               |    |

| Configuración de PVM para WIN32                              |    |

| RSHD – Remote Shell Deamon                                   |    |

| E: Regresión lineal                                          |    |

| Estimación de los parámetros del modelo                      |    |

| Estimación de $\sigma^2$                                     |    |

| Intervalos de confianza                                      |    |

|                                                              |    |

| Intervalo de confianza de nivel $(1-\delta)$ para $\beta$    |    |

| Intervalo de confianza de nivel $(1-\delta)$ para $\alpha$   |    |

| Intervalo de confianza de nivel (1- $\delta$ ) para $\sigma$ | 99 |

| Bibliografia1 | 01 |

|---------------|----|

|               |    |

# 1. INTRODUCCION

La utilización de las computadoras para el cálculo científico y aplicaciones que procesan gran cantidad de datos, demandan un procesamiento con mejor rendimiento, bajo costo y una buena producción. Por estos motivos se está incrementando la aceptación y adopción del cómputo paralelo. Los mayores desarrollos en el procesamiento paralelo tuvieron lugar en los procesadores paralelos (PP) y el cómputo distribuído.

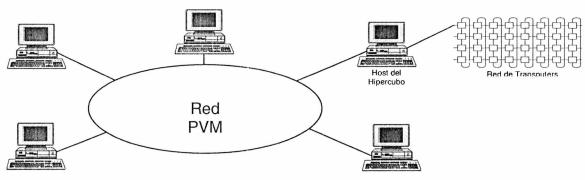

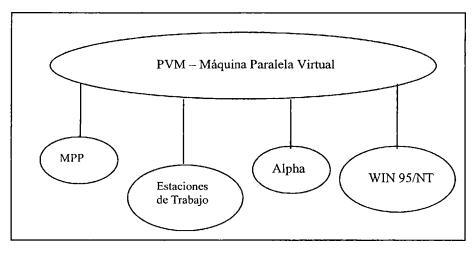

Uno de los procesadores paralelos más utilizados son las multicomputadoras basadas en transputers, que combina un conjunto de procesadores RISC con capacidad de interconexión flexible. En el cómputo distribuído un conjunto de computadoras, no necesariamente homogéneas, que pueden ser conectadas a una red son utilizadas para resolver un problema en forma conjunta. El sistema PVM (Parallel Virtual Machine) por ejemplo utiliza el modelo de pasaje de mensaje para permitir a los programadores realizar cómputo distribuído en una amplia variedad de tipos de computadoras, incluyendo PP.

En el campo del procesamiento paralelo, la multiplicación de matrices (MM) es uno de los benchmarks más conocidos, estudiados y aceptados. Tiene aplicaciones en diversas áreas, como por ejemplo el procesamiento de imágenes y aplicaciones que incluyen la resolución de problemas de álgebra lineal.

Los algoritmos más reconocidos para la multiplicación de matrices en forma paralela requieren cómputo intensivo y gran capacidad de almacenamiento. Una grilla de transputers provee un medio propicio para distribuir la carga de cómputo y obtener un rendimiento razonable. Además, como posee memoria distribuida, puede procesar una carga mayor de datos en forma paralela.

Uno de los beneficios del cómputo distribuido es la utilización de hardware existente para reducir costos. La integración de la red de transputers a una red de estaciones de trabajo permite la participación de éstos en un cálculo intensivo, como lo es la multiplicación de matrices.

La presente tesis tiene dos objetivos:

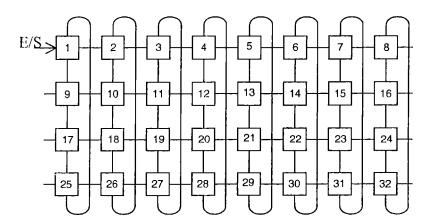

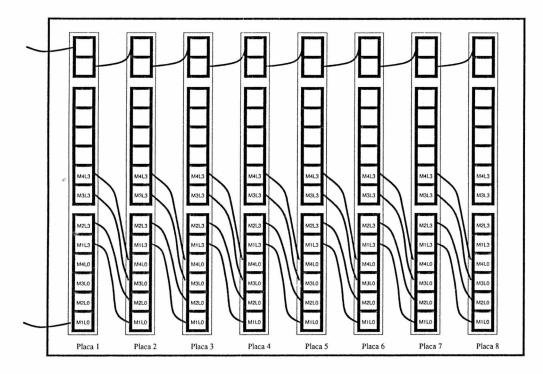

- Integrar una red de computadoras (estaciones de trabajo) entre las que se encuentra un hipercubo de 32 transputers (T805) conectados en forma de grilla. De esta manera se obtiene una máquina paralela "global".

- Desarrollar una aplicación correspondiente al ámbito científico en la máquina paralela. La aplicación elegida fue la multiplicación de matrices.

A partir del presente trabajo se podrán obtener distintas medidas de personnance de la multiplicación de matrices en la máquina paralela y tiempos de comunicación requeridos para la integración de los distintos tipos de computadoras.

# 1.1. Procesamiento Paralelo

En el amplio espectro de problemas resueltos por computadoras, existen dos en particular: los inherentemente paralelos que necesitan cómputo paralelo y aquellos que requieren procesar grandes cantidades de datos. Entre los inherentemente paralelos podemos encontrar productor y consumidor, lectores y escritores, entre otros. Entre los que requieren el procesamiento masivo de datos podemos encontrar aplicaciones para el manejo de datos enviados por un satélite, verificación y prueba de modelos de aviones y astronomía, entre otros.

El vertiginoso desarrollo de la tecnología describe un avance exponencial en la velocidad de procesamiento en los procesadores. Pero existe un límite: la velocidad de la luz en el vacío. Ninguna computadora por más velocidad de procesamiento que posea no podrá igualar a la velocidad obtenida en una colección de procesadores utilizados en forma conjunta para resolver un problema en particular.

De este modo llegamos a la conclusión de que la única forma de tratar algunos problemas es por medio del procesamiento paralelo. Si varias operaciones pueden ser ejecutadas simultáneamente, el tiempo total de procesamiento se verá reducido, aún cuando cada una de las operaciones no se lleve a cabo más rápidamente [Tin98]. En el procesamiento paralelo, esta simultaneidad se logra ejecutando al mismo tiempo un conjunto de pequeñas tareas que resuelven un problema de gran escala [Gei94].

El éxito del procesamiento paralelo se debe a dos de los mayores desarrollos en esta área: los procesadores paralelos (PP) y el cómputo distribuido.

Los procesadores paralelos pueden combinan cientos de procesadores en un único gabinete y conectados a cientos de gigabytes de memoria. Ofrecen un enorme poder de cómputo y son las computadoras más poderosas del mundo. Todos los procesadores poseen las mismas características. O sea se tiene una colección homogénea de procesadores.

En cómputo distribuido un conjunto de computadoras conectadas por una red son usadas colectivamente para resolver un problema de gran escala. La combinación de varias estaciones de trabajo en una red de alta velocidad puede tener mayor poder de procesamiento que una única supercomputadora.

Empezaremos definiendo la operación multiplicación de matricess y la forma de paralelizarla y para luego pasar al estudio del procesamiento paralelo con un conjunto de definiciones que facilitarán el estudio de los siguientes capítulos. Luego estudiaremos las arquitecturas de procesamiento paralelo para obtener una programación óptima ante una computadora paralela dada.

# 1.2. Multiplicación de matrices

Se quiere obtener la multiplicación de matrices [Gei95]

$$C = AB$$

Asumimos que cada matriz X tiene las dimensión  $m^X \times n^X$ ,  $X \in \{A,B,C\}$ . Se tienen las restricciones en estas dimensiones para que la multiplicación este bien formada: asumiremos que las dimensiones de C son  $m \times n$ , mientras que la otra dimensión es k.

Asumimos la siguiente asignación de datos a los nodos: dada una matriz  $m^X \times n^X$ ,  $X \in \{A,B,C\}$ , y una grilla lógica  $r \times c$  de nodos, particionaremos de la siguiente manera:

$$X = \left(\begin{array}{c|c} X_{00} & \dots & X_{0(c-1)} \\ \hline \vdots & & \vdots \\ \hline X_{(r-1)0} & \dots & X_{(r-1)(c-1)} \end{array}\right)$$

asignando  $X_{ij}$  al nodo  $\mathbf{P}_{ij}$ . La submatriz  $X_{ij}$  tiene las dimensiones  $m_i^X \times n_j^X$  con?  $m_i^X = m$  y?  $n_i^X = n$ . Si  $a_{ij}$ ,  $b_{ij}$ ,  $c_{ij}$  denotan el elemento (i,j) de las matrices, respectivamente, entonces los elementos de C estan dados por la siguiente operación

$$c_{ij} = ? a_{ik} b_{kj}$$

Las filas de C se calculan de las filas de A, y las columnas de C se calculan de las columnas de B. Consideremos que cálculo se requiere para formar  $C_{ij}$ :

$$C_{ij} = \left( A_{i0} \mid A_{iI} \mid \cdots \mid A_{i(c-I)} \right) \quad \left( \frac{B_{0j}}{B_{lj}} \right)$$

$$B^{j}$$

$$B^{j}$$

Notar que  $A'_i$  está enteramente asignado al nodo fila i, mientras que  $B'^j$  está asignado al nodo columnna j. Teniendo

$$A'_{i} = \left(a'_{i}^{0} \middle| a'_{i}^{I} \middle| \dots \middle| a'_{i}^{(k-l)}\right) \quad y \left(\frac{b'_{0}^{T}}{b'_{f^{T}}}\right) \left(\frac{b'_{0}^{T}}{b'_{(r-l)}}\right)^{T}$$

vemos que

$$C_{ij} = \underset{l=0}{\overset{k-1}{?}}_{l=0} a_{i}^{l} b_{i}^{l}$$

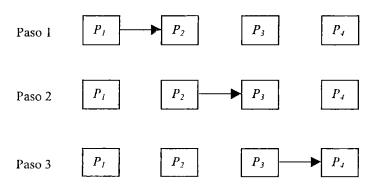

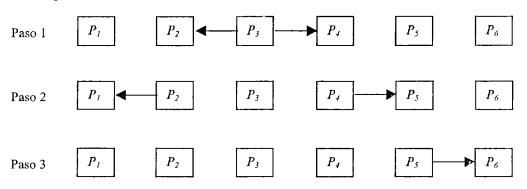

La multiplicación matriz-matriz puede ser formulada como una secuencia de una actualización. Cada una de estas actualizaciones pueden ser paralelizadas. El pseudo-código para esta paralelización se muestra en la figura 1.1, ejecutándose simultáneamente en todos los nodos  $P_{ii}$ .

```

C_{ij} = 0

for l = 0, k - 1

broadcast de a_i^{l} en mi fila

broadcast de b_i^{l} en mi columna

C_{ij} = C_{ij} + a_i^{l} b_i^{l}

```

figura 1.1: Pseudo-código para C = AB.

# 1.3. Definiciones Generales

A continuación se detallan un conjunto de definiciones generales [TIN98a] que ayudarán al entendimiento del léxico del informe.

Paralelismo: Ejecución simultánea (en el mismo instante de tiempo) sobre diferentes componentes físicos (procesadores). El paralelismo es un concepto asociado con la existencia de múltiples procesadores ejecutando un algoritmo en forma coordinada y cooperante. Al mismo tiempo se requiere que el algoritmo admita una descomposición en múltiples procesos ejecutables en diferentes procesadores (concurrencia).

# Objetivos del Procesamiento Paralelo:

- Disminuir los tiempos de ejecución.

- Incrementar la eficiencia.

- Atender fenómenos del mundo real que suceden en paralelo.

**Proceso y Procesador:** Un proceso es un bloque de programa secuencial, con su propio seguimiento de control. El concepto de proceso es el concepto básico e inicial de la programación concurrente: si en el sistema existen procesos independientes, existe la concurrencia. Cada proceso puede residir en un procesador independiente o dedicado. También se pueden tener múltiples procesos sobre el mismo procesador. Se debe notar que en este último caso se tiene concurrencia pero no paralelismo, o simultaneidad de ejecución.

Interacción, Comunicación y Sincronización de procesos: N procesos que residen en un procesador o en varios procesadores interactúan para ejecutar los aspectos del algoritmo global que requieran cooperación.

La interacción requiere comunicación para el intercambio de datos entre los procesos. La comunicación entre dos procesos puede ser por memoria compartida, a través de un mensaje explícito entre los procesos, o de un mensaje implícito por medio de un proceso servidor intermedio.

Cuando dos procesos necesitan ajustar el orden de ejecución de sus secuencias de instrucciones al estado de la ejecución del otro, se deben sincronizar.

Speed-Up (o Factor de Speed-Up): La relación entre el mejor tiempo de ejecución de un algoritmo sobre un procesador  $(T_I)$  y el tiempo de ejecución sobre una arquitectura paralela con N procesadores  $(T_N)$  se denomina factor de Speed-Up (S).

$$S = T_1 / T_N$$

- El óptimo que se puede esperar para S es N.

- Normalmente, resulta prácticamente imposible alcanzar el óptimo.

- Además, parece razonable pensar que más allá de un cierto N, para un dado problema algorítmico PA, las ineficiencias propias del algoritmo harán inútil el agregado de nuevos procesadores, es decir que S tendrá una cota máxima distinta de N.

*Eficiencia*: La relación entre el Speed-Up alcanzado S y el óptimo teórico *Sop* se define como eficiencia (E).

$$E = S / Sop$$

O, lo que es igual,

$$E = S / N$$

tal como se la encuentra definida en (Kum94), y donde N representa la cantidad de procesadores. Es claro que

$$E \leq 1$$

La eficiencia depende normalmente del tamaño del problema, tal como sucede con el factor de Speed-Up. En este factor de eficiencia están englobados varios aspectos, como el balance de la carga computacional. Cuando la carga computacional de la aplicación está balanceada, se obtiene un grado de ocupación similar en cada uno de los procesadores que forman parte de la arquitectura paralela. El desbalance de carga tiende a secuencializar la ejecución de la solución algorítmica.

Para lograr un rendimiento cercano al óptimo, o el óptimo, es necesario que confluyan tres aspectos en la utilización de las computadoras paralelas:

- 1. Capacidad de procesamiento del hardware.

- 2. Capacidad de programación paralela (software) sobre el hardware.

- 3. Aplicación paralelizable.

# 1.4. Arquitecturas de Procesamiento

A continuación se dará una breve descripción de la clasificación de las arquitecturas de procesamiento paralelo. Esta clasificación fue establecida por Flynn en 1972 [Tin98], aunque no cubre todas las diversidades de computadoras modernas, es aún utilizada porque impone un orden y mantenimiento de un nivel de simplicidad necesario para las arquitecturas de hoy en día. La categorización establecida por Flynn está basada en la forma en que la arquitectura administra el flujo de instrucciones que operan sobre los datos. Define cuatro categorías: SISD, MISD, SIMD, MIMD.

En la categoría SISD (Single Instruction Single Data) se encuentra la computadora clásica de procesamiento secuencial, definida por Von Neumann. Las instrucciones se ejecutan una después de otra, en serie. Poseen una sola unidad de control, una sola unidad de procesamiento y una única memoria.

En el caso de la categoría MISD (Múltiple Instruction Single Data) un mismo dato es procesado por múltiples instrucciones en distintas unidades de procesamiento. Este tipo de arquitecturas se adapta a una clase de problemas y no se considera de propósito general.

En la categoría SIMD (Single Instruction Multiple Data) las computadoras poseen un conjunto de elementos de procesamiento idénticos, todos controlados por una única unidad de control. Cada elemento de procesamiento procesa dato/s distinto/s de los demás.

Las computadoras de la categoría MIMD (Multiple Instruction Multiple Data) se consideran intrínsecamente paralelas y es aceptada como de propósito general. Las computadoras que se incluyen dentro de esta categoría constan de n procesadores, en donde cada procesador pertenece a la categoría SISD. Por esta razón, cada uno de los procesadores puede ejecutar su propia secuencia de instrucciones, y cada secuencia de instrucciones actúa con diferentes datos de los demás procesadores. La forma en que se conectan los procesadores a la memoria y también entre sí permite diferenciar al menos dos subclases: multiprocesadores y las multicomputadoras.

En los multiprocesadores, todos los procesadores comparten el mismo espacio de memoria, por este motivo también se las conoce como computadoras fuertemente acopladas. La comunicación entre los procesadores se realiza por medio de la memoria compartida, requiriendo para esto último mecanismos de sincronización.

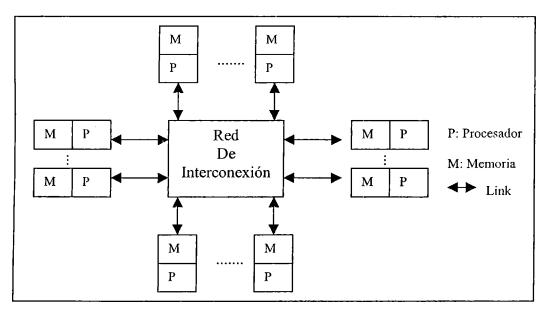

En las multicomputadoras cada procesador posee su propia memoria (exclusiva) y se comunica con los demás procesadores por medio de mensajes explícitos a través de una red de interconexión. También reciben el nombre de computadoras débilmente acopladas, multicomputadoras de pasaje de mensajes y también computadores con arquitectura de memoria distribuida. En la figura 1.2 se muestra una arquitectura MIMD con memoria distribuida.

Figura 1.2: Arquitectura MIMD con Memoria Distribuida [Tin98]

# 1.5. Organización del informe

El informe está organizado de la siguiente manera:

- Capítulo 1: Introducción al problema a resolver. Definición del procesamiento paralelo y definiciones asociadas con éste. Breve descripción de las distintas arquitecturas de procesamiento paralelo.

- Capítulo 2: Redes de computadoras heterogéneas. Tipos, ventajas y problemas asociados. Sistema PVM.

- Capítulo 3: Definición de transputer, su arquitectura y sus características.

- Capítulo 4: Algoritmos de multiplicación de matrices. Definición de Single Program Multiple Data (SPMD). Descripción y comparación de los algoritmos SUMMA y DIMMA.

- Capítulo 5: Diseño del algoritmo de MM. Diseño del modo SPMD. Descripción de los procesos de ruteo de datos y de procesamiento.

- Capítulo 6: Detalles de implementación de los algoritmos de MM, procesos de ruteo de datos y de procesamiento. Deadlock. Buffering. Mensajes. Dimensión de las matrices. Pasaje de parámetros.

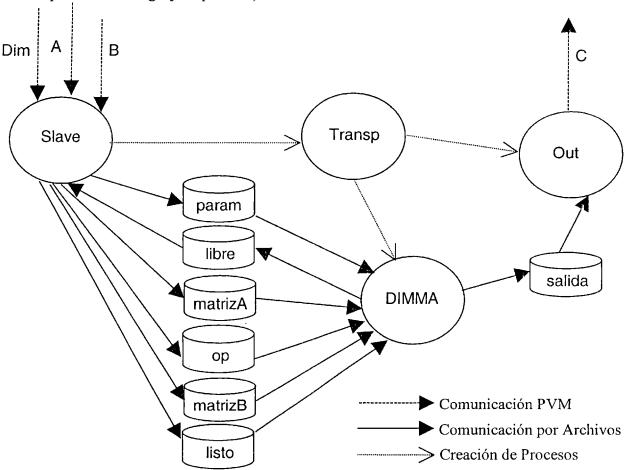

- Capítulo 7: Integración de la red transputers con PVM. Idea general. Integración de los transputers a la red de computadoras. Pasaje de parámetro en la máquina paralela

- "global". Pasaje de parámentros. Entrada y salida del hipercubo a la red. Comunicación con PVM. Algoritmo de MM global.

- Capítulo 8: Resultados Obtenidos: tiempos empleados en el algoritmo, speed-up, tiempos de comunicación. Objetivos logrados. Trabajo futuro.

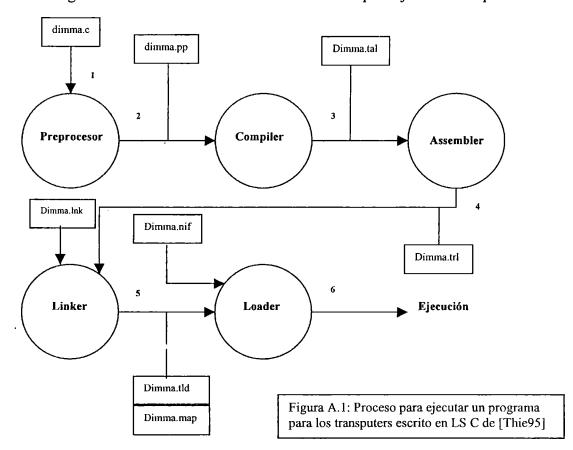

- **Apéndice A:** Lenguaje 'C' paralelo. Rutinas para especificación de concurrencia y semáforos. Manejo de canales físicos y virtuales. Timing y Scheduling.

- Apéndice B: Librería de PVM. Rutinas para la administración de procesos y comunicación.

- **Apéndice C:** Configuración del hipercubo en forma de grilla. Placas *VME-XP*<sup>TM</sup>. Utilización de los jumpers. Hardwired Link Configuration Array. Configuración de la grilla.

- Apéndice D: Instalación del sistema PVM para WIN32 e integración con LINUX.

- Apéndice E: Regresión lineal. Parámetros  $\alpha$  y  $\beta$ .

# 2. Redes de computadoras heterogéneas

En la actualidad las empresas o instituciones conectan un conjunto de estaciones de trabajo para compartir recursos, tales como datos o dispositivos caros, aunque no es la única utilidad que se les puede dar. Un conjunto de estaciones de trabajo (workstations) interconectadas en una LAN cooperando para resolver un problema tiene un costo más bajo, con respecto al rendimiento que los procesadores paralelos. Esta forma de resolución de problemas de cómputo intensivo se ha denominado cómputo paralelo sobre NOW (Network Of Workstations) [TIN98a].

En un procesador paralelo (PP), cada procesador es exactamente como los demás en capacidad, recursos, software, y velocidad de comunicación. Las computadoras disponibles en una red pueden haber sido hechas por diferentes vendedores o tener diferentes compiladores. Por lo que es necesario tener en cuenta los distintos tipos de heterogeneidad a la hora de programar:

- arquitectura,

- formato de los datos,

- velocidad de procesamiento,

- carga de la máquina, y

- carga de la red.

Cada tipo de arquitectura tiene su propio método óptimo de programación. La máquina paralela virtual puede estar compuesta de computadoras paralelas. Aún cuando la arquitectura sea sólo de workstations seriales, existe el problema de incompatibilidad en los formatos binarios y la necesidad de compilar una tarea paralela en cada máquina diferente.

Los formatos de los datos en computadoras diferentes a menudo son incompatibles, Esta incompatibilidad es un punto importante en el cómputo distribuido porque los datos enviados por una computadora pueden ser ilegibles en la computadora receptora.

En general, los problemas relacionados con el hardware están básicamente resueltos por los protocolos estándares de comunicación como TCP/IP junto con ambientes como PVM e implementaciones de MPI que se encargan de evitar que la heterogeneidad llegue a ser visible desde los programas paralelos.

Aún si el conjunto de computadoras son todas workstations con el mismo formato de datos, se pueden tener diferentes velocidades de procesamiento. La máquina virtual puede estar compuesta de un conjunto idéntico de workstations. Pero la red de computadoras puede tener otros usuarios ejecutando distintos trabajos, por lo que la carga de cada máquina puede variar dramáticamente. Pueden existir estaciones de trabajo que permanecen sin procesamiento útil para ejecutar, lo cual no significa que las computadoras están siempre disponibles, aunque hay períodos en los cuales se puede considerar una disponibilidad completa de las estaciones de trabajo.

Como la carga de la máquina, el tiempo necesario para enviar un mensaje en la red puede variar dependiendo en la carga de la red impuesta por todos los demás usuarios, quienes no utilizan de la misma manera las computadoras de la máquina virtual. Este tiempo de envío es importante cuando una tarea se encuentra detenida esperando un mensaje, y aún más importante cuando el algoritmo depende del tiempo de arribo de los mensajes.

La paralelización de aplicaciones y la caracterización del rendimiento están fuertemente ligadas dado que el beneficio o perjuicio que se obtiene utilizando una máquina paralela se cuantifica en función de los índices de rendimiento que se utilizan. Si los índices de rendimiento son correctos (no ocultan información), el "mejor" programa paralelo dará la justificación para utilizar o no una red de estaciones de trabajo para resolver un problema.

Los índices de rendimiento para carcterizar una NOW están basados en las nociones de factor de *speedup* y MFLOPS (Millones de operaciones de punto flotante por segundo). Esta segunda medida es particularmente útil en el área de los problemas de cómputo intensivo (cálculo numérico).

A pesar de las dificultades causadas por la heterogeneidad, el cómputo distribuido tiene las siguientes caracteristicas:

- Por la utilización de hardware existente, el costo de cómputo puede ser muy bajo.

- El rendimiento puede ser optimizado asignando cada tarea en la arquitectura más apropiada.

- Posibilidad de explotar la naturaleza heterogénea de un cómputo.

- Los recursos de la computadora virtual pueden crecer por etapas y adquirir la última tecnología en cómputo y redes.

- El desarrollo de programas se puede acrecentar usando un ambiente familiar. Los programadores pueden utilizar editores, compiladores, y debuggers que están disponibles en máquinas individuales.

- Las computadoras individuales y workstations son generalmente estables, y se tiene experiencia en un uso confiable.

- La tolerancia a fallas a nivel de usuario y nivel de programa puede ser implementada con poco esfuerzo tanto en la aplicación como en el sistema operativo subyacente.

- El computo distribuido puede facilitar el trabajo colaborativo.

Todos estos factores se trasladan en la reducción del tiempo de desarrollo y corrección, reducción de la disputa por los recursos, costos reducidos, y posiblemente implementaciones más eficientes de una aplicación.

# 2.1. Introducción a PVM

PVM es un sistema que posibilita desarrollar programas paralelos en forma eficiente y sencilla utilizando un hardware ya existente [Gei94]. Permite que una colección de computadoras heterogéneas sean vistas como una simple máquina virtual

paralela (*Parallel Virtual Machine*). El ruteo de mensajes, la conversión de datos y la administración (scheduling) de tareas es realizada transparentemente por PVM, facilitando el uso de la red conformada por computadoras de diferentes arquitecturas.

El modelo de computación de PVM es simple y general. La interface de programación no es complicada, lo que permite que los programas sean implementados en forma simple e intuitiva. Una aplicación consta de una colección de tareas (tasks) que se ejecutarán en la red que conforma la máquina virtual. Los recursos de PVM son accedidos por estas tareas mediante una librería que contiene la interface estándar de las rutinas. Estas rutinas permiten la creación y terminación de las tareas como así también la sincronización entre éstas. Las primitivas de pasaje de mensajes de PVM posibilitan la comunicación de computadoras heterogéneas, usando constructores fuertemente tipados para realizar buffering y la transmisión. Estas primitivas de comunicación incluyen constructores para enviar y recibir datos, así como también primitivas de alto nivel como broadcast, sincronización con barreras, y suma global.

Una tarea, durante su ejecución, puede iniciar o terminar otra tarea o agregar o eliminar computadoras de la máquina virtual. Además, cualquier proceso puede comunicarse o sincronizare con cualquier otro.

# 2.2. El Sistema PVM

PVM es un conjunto integrado de herramientas y librerías que emulan un ambiente de cómputo concurrente en forma heterogénea, flexible y de propósito general sobre computadoras con distintas arquitecturas interconectadas por una red. El objetivo de PVM es permitir que esta colección de computadoras sean usadas cooperativamente para computaciones paralelas o concurrentes. PVM se basa en los siguientes principios:

- "Host pool" configurado por el usuario: Las tareas que forman parte de la aplicación se ejecutan en un conjunto de máquinas determinadas por el usuario para una dada ejecución del programa PVM. Estas máquinas pueden ser multiprocesadores (con memoria compartida o distribuida) o una máquina con una sola CPU. Este "host pool" (colección de computadoras que forman la máquina virtual) puede ser alterado durante la ejecución de una aplicación (una característica importante para la tolerancia a fallas).

- Acceso transparente al hardware: Los programas de aplicación pueden ver el hardware como una colección de elementos de procesamiento virtuales sin atributos particulares (no le interesa los detalles de la arquitectura); o puede aprovechar las características de algunas máquinas, cargando ciertas tareas en la computadora que sea más apropiada para su procesamiento.

- Computación basada en el Proceso: La unidad de paralelismo en PVM es una tarea, un hilo (thread) de control secuencial e independiente que alterna entre comunicación y computación. No necesariamente una sola tarea se puede ejecutar en un procesador, sino que múltiples procesos pueden coexistir en un mismo procesador.

- Modelo de pasaje de mensajes explícito: el conjunto de tareas que forman la aplicación cooperan explícitamente enviando y recibiendo mensajes unas con otras. El tamaño de un mensaje está limitado sólo por la memoria disponible.

- Soporte heterogéneo: PVM soporta heterogeneidad a nivel de máquinas, redes, y aplicaciones. Con respecto al pasaje de mensajes, PVM posibilita que mensajes con

más de un tipo de datos sean intercambiados entre máquinas con distintas representaciones de datos.

• Soporte de Multiprocesadores: PVM utiliza las facilidades de pasajes de mensajes nativas de los multiprocesadores para aprovechar su hardware específico.

El sistema PVM está compuesto por dos partes. La primer parte es un "daemon" llamado *pvmd3* (se abrevia como *pvmd*) que reside en todas las computadoras que conforman la máquina virtual. La segunda parte del sistema es una librería con la interface de las rutinas de PVM. Esta librería contiene un repertorio funcionalmente completo de las primitivas necesarias para la cooperación entre tareas en una aplicación.

El modelo de computación de PVM se basa en la noción de que una aplicación consiste de varias tareas. Cada tarea es responsable de una parte de la aplicación. Una forma de paralelizar una aplicación es según su función; es decir que cada tarea tiene una función distinta, llamado paralelismo funcional. Otro método común de paralelizar una aplicación consiste en que todas las tareas son la misma, pero actúan sobre diferentes datos, llamado paralelismo de datos. Esto también se conoce como el modelo de computación SPMD (Single Program Multiple Data).

PVM actualmente soporta los lenguajes C, C++ y Fortran. Esto se debe a que la mayoría de las aplicaciones que pueden aprovechar las capacidades de PVM están implementadas con C y Fortran, y además se agrega C++ por la tendencia emergente de experimentar con lenguajes y metodologías orientadas a objetos.

Las tareas de PVM son identificadas con un número entero llamado *identificador* de tarea (task identifier, TID). Estos TIDs son suministrados por el pvmd local, y son únicos en la máquina virtual. Los mensajes son enviados y recibidos por medio de estos TIDs, por lo cual PVM provee rutinas para retornar estos valores.

También se pueden generar grupos de tareas. Cuando una tarea se une a un grupo se le asigna un número de instancia único en ese grupo. Las funciones de grupo son implementadas por PVM de forma que sean transparentes al usuario. Los grupos pueden superponerse, y las tareas pueden enviar mensajes en forma de broadcast a grupos de los que no son miembros.

El paradigma general para la programación de una aplicación en PVM es el siguiente. El usuario escribe uno o más programas secuenciales en C, C++ o Fotran 77 que contienen llamadas a la librería de PVM. Cada programa corresponde a una tarea que conforma la aplicación. Estos programas son compilados para cada arquitectura en el "host pool", y los archivos ejecutables generados son colocados en un lugar accesible por PVM. Para ejecutar una aplicación, el usuario inicia una tarea (generalmente el "master" o la tarea inicial) manualmente en la máquina del "host pool". Este proceso iniciará otras tareas de PVM, obteniendo una colección de tareas activas que intercambiarán mensajes para resolver el problema.

# 3. EL TRANSPUTER

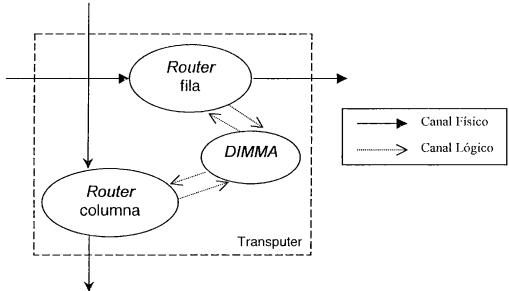

Las computadoras basadas en transputers son máquinas MIMD, más precisamente multicomputadoras. Pertenecen a la categoría de las arquitecturas de pasaje de mensajes, en donde los transputers intercambian información unos con otros y no es posible tener acceso remoto a la memoria de otro transputer.

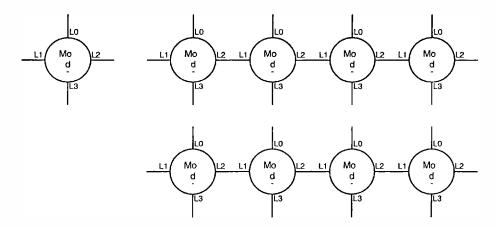

Para poder hacer efectivo el envío de mensajes es necesario poseer una red de interconexión para conectar los transputers. Esta red define la topología de conexión de los transputers. El intercambio de información se realiza por medio de los enlaces de comunicación (links) y en general en las máquinas MIMD son estáticos. Los transputers están conectados directamente y cada transputer posee la misma cantidad de enlaces.

# 3.1. Características de un transputer

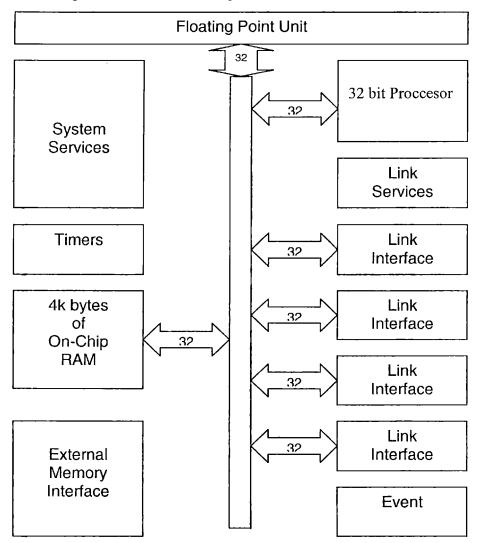

El circuito de un transputer contiene un procesador, una pequeña cantidad de memoria, un coprocesador y cuatro links bidireccionales de alta velocidad [Thi95]. Aunque esta lista no impresiona, el diseño de un transputer provee el ambiente necesario para el procesamiento paralelo.

# **Procesador Multitasking**

El procesador de un transputer soporta multitasking, y fuerza dos niveles de prioridad para tareas concurrentes. Por lo que en una misma aplicación podemos tener procesamiento concurrente y paralelo. El procesamiento concurrente dentro de un mismo transputer y procesamiento paralelo a través de un conjunto de transputers.

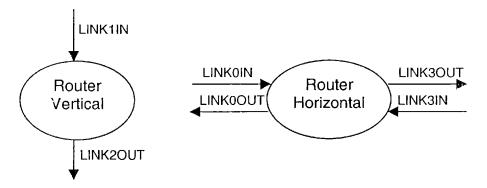

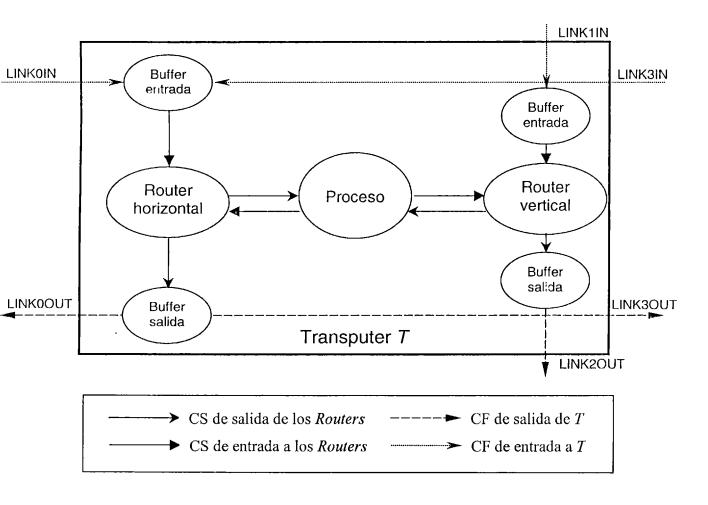

# Comunicación por medio de links y canales

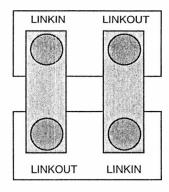

La comunicación entre transputers es realizada vía links seriales de alta velocidad. El reducido número de alambres de comunicación requeridos y la simplicidad del protocolo hace que la interconexión de los transputers sea simple y en la mayoría de los casos configurable por el usuario. A nivel de software, los links de hardware son definidos como *canales*. Los transputers se comunican por medio de links, las tareas lo hacen por medio de canales. Las primitivas de comunicación son implementadas directamente en microcódigo y el acceso a los links seriales es mapeado a memoria. Por lo que las primitivas para comunicar transputers vecinos son las mismas que para comunicar tareas.

# Canales virtuales

Sólo aquellos transputers que están conectados directamente pueden intercambiar mensajes. El lenguaje C paralelo [Log94a][Log94b] posibilita la definición de canales virtuales, que permiten la transferencia de mensajes entre diferentes transputers como si estuvieran conectados por un canal, a pesar de que no estén conectados. Crea un camino virtual que conecta, en forma transparente al usuario, cualquier par de transputers.

# 3.2. Arquitectura de un transputer

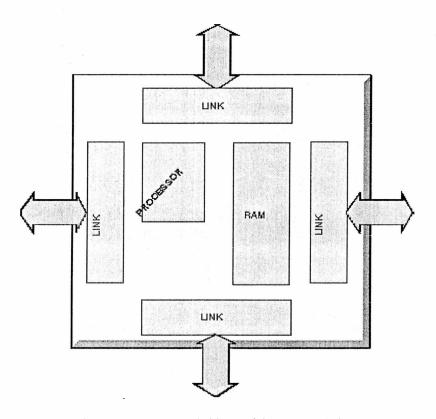

El circuito es una computadora (computer) en sí mismo, con un procesador, memoria para almacenar datos y programas, y varios ports para el intercambio o transferencia de información con otros transputers o hacia el exterior. Por el diseño de éstos circuitos que pueden ser conectados de la misma manera como los **trans**itores en una computadora, nació **transputer**. El diagrama del bloque de un transputer se muestra en la figura 3.1.

Figura 3.1: Diagrama de bloque del transputer [Thi95]

El término *transputer* realmente abarca una familia de circuitos: algunos con un tamaño de palabra de 16 bits (la serie T2xx), otros con un tamaño de palabra de 32 bits (T805, T800, T425, T414, y el T400). Las series T4xx y T8xx difieren una de otra en varios factores:

- La cantidad de memoria on-chip. El T414 y T400 tienen solo 2Kbytes de memoria interna, mientras que la serie T8xx tiene 4 Kbytes.

- Contienen un procesador de punto flotante. En el T800 y T805 está integrado, mientras que la serie T4xx posee un software que implementa (a una velocidad más lenta) las operaciones de punto flotante.

- El número de ports de E/S disponibles. La serie T4xx tiene dos, mientras que la serie T8xx tiene cuatro, permitiendo redes más complejas.

# 3.3. El procesador

El rendimiento obtenido por los transputers se debe a las siguientes decisiones de diseño:

No tiene registros dedicados a los datos. Posee una pila de registros, la cual permite una selección implícita de los registros. El resultado obtenido es un pequeño formato de instrucción.

Conjunto de instrucción reducido. El transputer adopta la filosofía RISC y dispone de un pequeño conjunto de instrucciones que se ejecutan con unos pocos ciclos de reloj.

Disponibilidad de multitasking en microcódigo. Las acciones necesarias para que el transputer cambie de una tarea a otra son ejecutadas a nivel de hardware, liberando al sistema del programador de esta tarea, y resultando en rápidas operaciones de cambio.

Se estudiarán estas tres características basadas en el Inmos T800. El diagrama de bloque del transputer se muestra en la figura 2.2.

Figura 3.2: Diagrama de bloque de un transputer

# Operación basada en pila

El procesador posee seis registros. Tres (los registros A, B y C) son usados como registros de datos e implementan una pila. No es necesario especificar qué registro del procesador recibirá los datos. El procesador toma los datos uno tras otro de la pila y apila el resultado de la operación.

La ventaja de operar con una pila de datos radica en que elimina la necesidad de agregar bits extras en la instrucción para especificar el registro al que debe acceder. Como resultado, las instrucciones pueden ser empaquetadas en palabras más pequeñas, caben mejor en memoria, y se pierde menos tiempo para recuperar las instrucciones de memoria.

# Multitasking

El proceso por el cual un procesador divide su tiempo entre varios programas ejecutándose al mismo tiempo se llama *multitasking*. Multitasking es una las formas más importantes de mejorar la performance de un procesador permitiendo comenzar otro programa si uno de los que se está ejecutando actualmente no puede seguir por un tiempo, porque por ejemplo realiza una operación de E/S.

Multitasking es la primera forma de paralelismo disponible por el transputer, y la realiza manteniendo una *lista de tareas* que se deben ser ejecutadas. En cualquier momento una tarea de un transputer puede encontrarse en alguno de estos estados:

# Activa

En este estado la tarea se está ejecutando o está en la lista de tareas esperando a ser ejecutada.

#### Inactiva

La tarea no está en la lista de tareas activas, no puede ejecutarse por una de las siguientes condiciones:

- La tarea está esperando por una entrada en uno de los ports de E/S

- La tarea está esperando por una salida en uno de los ports de E/S

- La tarea pasó a estar inactiva por un periodo de tiempo determinado.

# Tareas activas

El transputer mantiene las tareas activas encadenadas en una lista enlazada, y dos de sus registros internos son usados para referenciar el frente y final de la lista. La lista actual es almacenada en memoria, y los registros contienen las direcciones de memoria de las celdas que definen la tarea. Para incrementar la flexibilidad y el poder del ambiente de multitasking, el transputer implementa dos niveles de *prioridad* para las tareas:

# Tareas de alta prioridad (nivel 0):

Una vez que obtienen el control del procesador, continúan ejecutándose hasta que terminan, o hasta que necesitan enviar información en un link serial.

# Tareas de baja prioridad (nivel 1):

Estas tareas se ejecutan cuando no hay ninguna tarea de alta prioridad activa, y se ejecutan durante un quantum de tiempo, intercambiando en un modelo round robin.

El transputer en realidad necesita mantener dos listas enlazadas, una para las tareas de baja prioridad y otra para las tareas de alta prioridad, y usa un total de cuatro registros para referenciar el frente y final de las listas.

# Rápido intercambio de tareas

El intercambio de tareas pertenecientes a la misma lista de prioridad o a diferentes listas de prioridad es manejado directamente por el procesador, y todos los registros que son actualizados son controlados internamente, por medio del microcódigo. Al eliminar esta acción del software perteneciente al kernel da como resultado que esta operación sea extremadamente rápida: menos de lus típicamente.

# Tareas inactivas

Si una tarea no puede continuar con su ejecución, el procesador la detiene y pasa a estar inactiva, ya sea porque expiró su quantum (evento del timer) o realizó una operación en un link. Al pasar al estado de inactiva, es eliminada de su lista enlazada y puesta en el workspace, el cual es un área de memoria.

# Timers y tareas inactivas

El T800 posee dos timers de 32 bit. Los timers se encuentran fuera de los procesadores como se muestra en la figura 3.2. Cada timer está asociado con una prioridad. Un timer, disponible para las tareas de alta prioridad, es incrementado cada microsegundo. El otro timer esta asociado con las tareas de baja prioridad y es incrementado cada 64 microsegundos.

# 3.4. Acceso a memoria

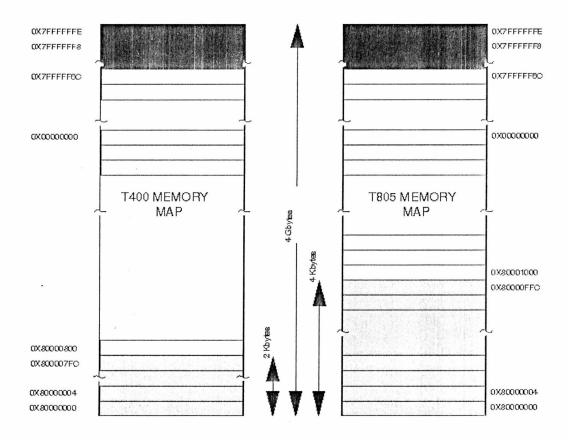

El transputer puede acceder a un espacio lineal de direcciones de 4Gbytes, correspondientes a los 32 bits de los registros de direcciones. De estos 4 Gbytes, 4Kbytes se encuentran dentro del circuito del transputer T805 (2 Kbytes en el T400), y corresponden a la parte baja del espacio de direcciones de la memoria.

Figura 3.3: Mapas de memoria de los transputers T400 y T800

El Inmos elige el mapeo de forma que las direcciones más bajas de memoria sean negativas, 0x80000000, mientras que la memoria más alta disponible es el entero más grande de 32 bit: 0x7FFFFFF. El rango 0x8000000 hasta 0x80000FFC (0x800007FC para el T400) corresponde a la memoria interna. 0x80001000, la dirección más baja de la memoria externa del T800 se la llama **MemStart** en la terminología de Inmos.

# Memoria wrap-around

En la mayoría de los sistemas, no todo el espacio de memoria disponible es utilizado. Por ejemplo, en el CSA Educational Kits, sólo I Mbyte de memoria externa es implementado, y sólo los 20 bits más bajos del bus de direcciones son usados. Esto resulta en un "wrap around" del espacio de direcciones de memoria. Como consecuencia el espacio de la pila o heap puede encontrarse fuera de la memoria física, produciendo resultados impredecibles.

En el ejemplo anterior los 12 bits más altos no son usados. Por lo que las direcciones que excedan los 20 bits serán tomadas nuevamente desde la dirección 0 en adelante. O sea, el procesador evita acceder a un espacio de direcciones no existente y para esto toma al espacio de direcciones en forma "circular".

# Rápida memoria interna

Para el transputer, el acceso a su memoria interna estática será aproximadamente 3 veces más rápida que el acceso a su memoria externa. Esta memoria interna deberá ser usada para almacenar los datos y códigos más usados, por ejemplo una pila del usuario.

Otro aspecto de la memoria interna es que afecta directamente el rendimento del sistema en la tasa transmisión de datos a través de los ports de E/S. La performance mejora si los datos a transmitir se encuentran en memoria interna; pero si no caben en ésta, obviamente la performance se degradará.

# 3.5. Los ports seriales de E/S

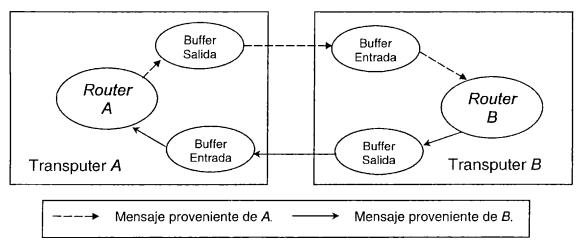

El transputer dispone de cuatro links seriales bidireccionales (dos en el caso del T400). Se utilizará el término link para referirnos a una conexión física entre dos transputers, y el término canal para describir una conexión de software entre dos procesos. La transferencia de datos en un link serial es *sincronizada* y *unbuffered*.

- Sincronización se refiere al hecho que si el proceso P1 ejecutándose en el transputer T1 necesita intercambiar (mandar o recibir) información con el proceso P2, entonces debe esperar hasta que P2 esté listo para participar en el intercambio. El proceso se dice que es sincronizado, el emisor no puede enviar sus datos hasta que el receptor no esté listo para aceptarlos, y viceversa.

- Comunicación unbuffered significa que ningún almacenamiento temporario es necesario para almacenar los mensajes entrantes o salientes. La transferencia se realiza directamente entre la memoria del emisor y la memoria del receptor.

Durante la comunicación, los procesos que inician la transferencia son **bloqueados**. Cada proceso es puesto al final de la lista de tareas inactivas. Debido a que el procesador y los links operan independientemente, el procesador es libre de ejecutar otro proceso cuando uno es bloqueado por comunicación. Si ocho de tales procesos requieren transferir en cada dirección de los cuatro links seriales, todos los links pueden ser activados simultáneamente, obteniendo un "throughput" equivalente al de ocho veces del "throughput" de un link. Como resultado los canales no requieren colas o buffers para los mensajes.

# Ports transparentes

Uno de los aspectos arquitecturales de más relevancia de los ports de E/S es que son *mapeados a memoria*. Esto significa que programar un port y pasarle la dirección y longitud del mensaje es realizado escribiendo estos números a posiciones de memoria que son mapcadas a los registros del port.

Como un resultado, las instrucciones que son usadas para programar los ports de E/S son todas instrucciones de lectura y escritura en memoria. Esto hace que estas instrucciones que acceden al link son las que se utilizan las direcciones que mapean a los registros del link. Si dos tareas que se están ejecutando en el mismo transputer,

ambas usando las mismas direcciones, pero una iniciando una salida y la otra una entrada, ambas pueden realizar la comunicación.

Distinguiremos entre canales de hard (comunicación entre procesos remotos) versus canales de soft (comunicación entre procesos locales al mismo transputer). Sólo el microcódigo sabrá la diferencia entre un canal de soft y un canal de hard. Las instrucciones del lenguaje Assembler no realizan la distinción, y por esta razón, tampoco el código de alto nivel.

Esto significa que un programa paralelo que posee varios procesos concurrentes puede ser adaptado con unos pocos cambios para que se ejecute en un sistema multitransputer.

# 3.6. Aspectos técnicos del CSA Educational Kit

Se describirá la versión IBM Personal Computer (PC) del CSA Transputer Educational Kit, que es el software de desarrollo utilizado para implementar la aplicación.

# Procesador adjunto

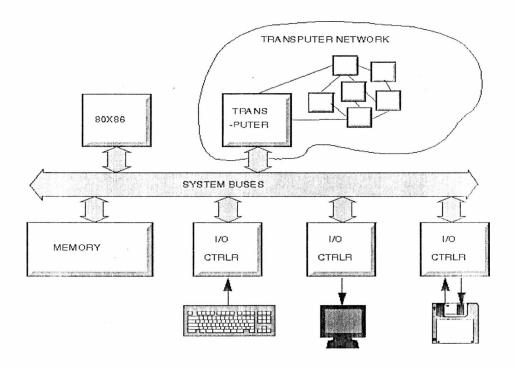

El sistema transputer opera como un *procesador adjunto* para la PC. Como tal, no reemplaza el procesador 80x86 en la PC, trabaja en conjunción con él. La PC se llama la *máquina host*, o simplemente *host*. Ningún software ejecutándose en la PC es afectado por la presencia de la red de transputers. En la figura 3.4 se muestra la arquitectura general de una PC con una red de transputers adjunta.

Figura 3.4: El transputer como un procesador adjunto

Uno de los transputers en la red es considerado un "conductor". En la mayoría de las veces se encuentra dentro de la PC, en uno de los slots ISA de E/S de 8 bit, por lo que puede tener acceso a los buses del sistema. Allí, se comporta como un despachador (dispacher), transferiendo información desde la PC hacia la red de transputers (programas y datos de entrada), o desde la red de transputers hacia el host (datos resultantes). A este transputer especial se lo llama transputer *PC-link*, o transputer *root*. El transputer root dedica uno de sus links para la comunicación con la PC.

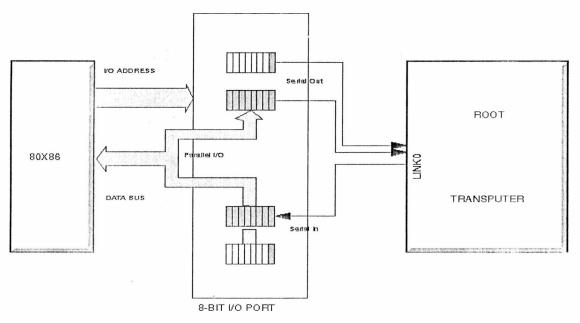

En algunos sistemas, el transputer root es localizado dentro de la máquina paralela, y la PC es equipada con una plaqueta de interface la cual implementa los ports de E/S como se muestra en la figura 3.5. Con este simple concepto de interface, la red de transputers puede ser conectada a varias PC's, o a una misma PC por medio de varias tarjetas de interface. Tales configuraciones, son para aplicaciones específicas como multiusuarios.

Figura 3.5: Interface de un port de 8 bits entre el host y el transputer root.

# Comportamiento de un port serial

La transferencia de información entre el host y el transputer root es administrada por el host como una operación de E/S estándar de 8 bit, muy similar a la comunicación con un port paralelo o RS232.

Cada acceso a los recursos de la PC debe ser a través de port de E/S de 8 bit, el cual es mantenido, por medio de software, por el 80x86. A veces el host será un simple subordinado del transputer root, atendiendo sus requerimientos y poniendo todos sus recursos a disposición del transputer. Otras veces, será más avanzado dividiendo el cómputo entre la red de transputers y el 80x86, y dejando las operaciones de E/S al último.

# 4. ALGORITMOS DE MULTIPLICACION DE MATRICES

Dadas dos matrices **A** y **B** se desea obtener la matriz producto **C**=**A**x**B**. Esta multiplicación se implementó utilizando el algoritmo DIMMA (Distribution-Independent Matrix Multiplication Algorithm) propuesto por Jaeyoung Choi [Cho].

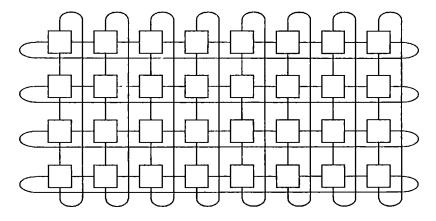

Los algoritmos clásicos de multiplicación de matrices [Kum94] se basan en una grilla de PxP procesadores, donde los bloques de las matrices son mapeados directamente a los procesadores. A diferencia de estos algoritmos, DIMMA y SUMMA (Scalable Universal Matrix Multiplication Algorithm) utilizan una distribución de bloques cíclica (ver más adelante) sobre una grilla de PxQ procesadores, con P y Q arbitrarios.

Primero se describirá la distribución de bloques cíclica y el modelo de cálculo. Luego se detallarán los algoritmos de SUMMA y DIMMA y una comparación de ambos.

# 4.1. Block Cyclic Data Distribution

La forma en la cual los datos son distribuidos en los procesadores en una computadora concurrente tiene un gran impacto en la rendimiento y escalabilidad de un algoritmo concurrente, ya que influye en las características de comunicación y en el balanceo de carga. La distribución de bloques cíclica (*block cyclic distribution* o también conocida como *block scattered*) [Cho92] [Cho94][Cho] provee una forma simple y de propósito general de distribuir una matriz particionada en bloques sobre una computadora concurrente con memoria distribuida.

Dada una malla de PxQ procesadores, una matriz es particionada en bloques de tamaño rxs; y los bloques separados por P filas de distancia, como así también a Q columnas de distancia son asignados al mismo procesador. Así, al procesador en la posición (p, q)  $(0 \le p < P, 0 \le q < Q)$  de la malla se le asignan los bloques cuyo índice es:

$$(p + iP, q + iQ)$$

donde  $i = 0, ..., (M_{bk}-p-1)/P$  y  $j = 0, ..., (N_{bk}-q-1)/Q$ , donde  $M_{bk}xN_{bk}$  es el tamaño de la matriz en bloques.

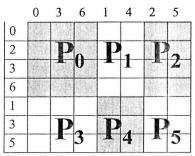

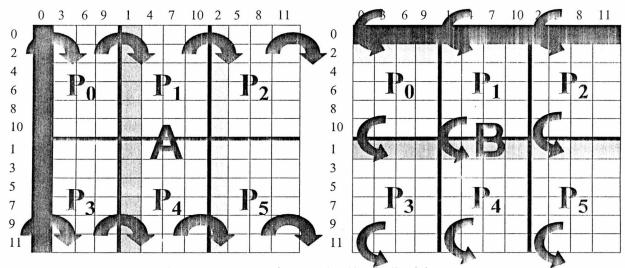

En la figura 4.1 se muestra un ejemplo de la distribución de bloques cíclica, donde una matriz de 7x7 bloques es distribuida sobre una grilla de 2x3 procesadores. Cada cuadrado dentro de la matriz (figura 4.1-a) representa un bloque de elementos, y el valor dentro de este bloque indica su posición en la grilla de procesadores. Todos los bloques etiquetados con el mismo número son asignados al mismo procesador. Los números a la izquierda y arriba de la matriz representan los índices de las filas y columnas de bloques, respectivamente.

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 2 | 0 | 1 | 2 | 0 |

| 1 | 3 | 4 | 5 | 3 | 4 | 5 | 3 |

| 2 | 0 | 1 | 2 | 0 | 1 | 2 | 0 |

| 3 | 3 | 4 | 5 | 3 | 4 | 5 | 3 |

| 4 | 0 | 1 | 2 | 0 | 1 | 2 | 0 |

| 5 | 3 | 4 | 5 | 3 | 4 | 5 | 3 |

| 6 | 0 | 1 | 2 | 0 | 1 | 2 | 0 |

a) distribución del punto de vista de la matriz

b) distribución del punto de vista de los procesadores

Figura 4.1: distribución de bloques cíclicas de una matriz de 7x7 bloques en una grilla de 3x4 procesdores

Como puede observarse en la figura 4.1(b), en este ejemplo no todos los procesadores reciben la misma cantidad de bloques. Esto se debe a que la cantidad de filas de bloques de la matriz no es múltiplo de la cantidad de filas de procesadores en la grilla y además la cantidad de columnas de bloques de la matriz no es múltiplo de la cantidad de columnas de procesadores en la grilla. La cantidad de bloques que reciben los procesadores difieren a lo sumo en una fila y/o una columna, pero todos los procesadores en una misma fila de la grilla tendrán la misma cantidad de filas de bloques, y los procesadores en una misma columna de la grilla tendrán la misma cantidad de columnas de bloques. Esto explica como la distribución de bloques cíclica balancea la carga de los procesadores. Este balanceo es a nivel de bloque, por lo cual si el tamaño de bloque es muy grande este balanceo no será tan real. Por ejemplo si los bloques fueran de tamaño 100 entonces las matrices de P<sub>0</sub> serán de 100 filas más que las matrices de los procesadores que se encuentren en otra fila de procesadores, como sucede con P<sub>5</sub>; lo mismo ocurre con las columnas. Con una distribución directa de bloques de la matriz a los procesadores, los procesadores de la última fila y última columna de la grilla tendrán porciones de la matriz mucho más pequeñas (especialmente el procesador de la última fila y última columna, como por ejemplo el procesador P<sub>5</sub> de la figura x 1,1 que tendrá sólo el bloque de la fila 6 y columna 6 de la matriz).

Esta forma de distribución también contribuye a la escalabilidad de los algoritmos que la utilizan. No impone ninguna restricción en cuanto a la cantidad procesadores en la grilla, el tamaño de las matrices y de los bloques dentro de cada matriz.

# 4.2. Modelo de cálculo

Para obtener la matriz producto C=A\*B, se asuma que A, B y C son de tamaño MxK, KxN, y MxN respectivamente. A su vez, el tamaño de los bloques de A es  $m_bxk_b$ , y los bloques de B y C son de  $k_bxn_b$  y  $m_bxn_b$  elementos, respectivamente. Por lo cual el número de bloques de las matrices A, B, y C son  $M_{bk}xK_{bk}$ ,  $K_{bk}xN_{bk}$ , respectivamente, donde  $M_{bk}=M/m_b$ ,  $N_{bk}=N/n_b$ , y  $K_{bk}=K/k_b$ .

# 4.3. SUMMA

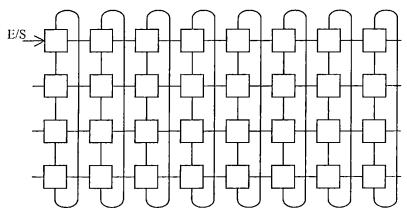

En SUMMA [Gei95], las matrices  $\mathbf{A}$  y  $\mathbf{B}$  son divididas en bloques de tamaño  $K_b$ , o sea que los bloques tienen igual cantidad de filas y columnas. Los procesadores multiplican la primera columna de bloques de  $\mathbf{A}$  con la primera fila de bloques de  $\mathbf{B}$ . Luego multiplican la próxima columna de bloques de  $\mathbf{A}$  con la próxima fila de bloques de  $\mathbf{B}$ , y así sucesivamente se repite el proceso para todas las columnas de  $\mathbf{A}$  y filas de  $\mathbf{B}$ , obteniendo así la matriz resultado  $\mathbf{C}$ .

Figura 4.2: Algoritmo SUMMA. Los bloques más obscuros son enviados primero y los más claros después.

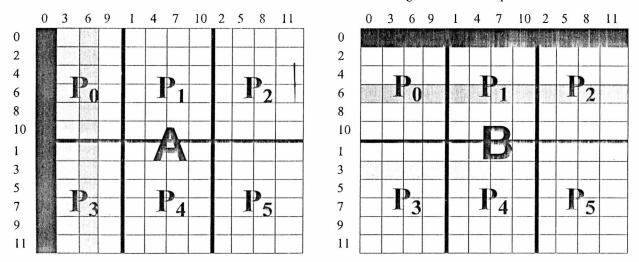

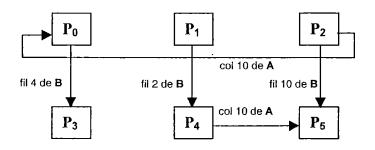

En la figura 4.2 se muestra un ejemplo de SUMMA, con una grilla de 2x3 procesadores, y la matrices A, B y C poseen 12x12 bloques. En el primer paso, la primera columna de procesadores, P<sub>0</sub> y P<sub>3</sub>, comienzan realizando un broadcast de la primera columna de bloques de A hacia cada fila de procesadores. Al mismo tiempo la primera fila de procesadores, P<sub>0</sub>, P<sub>1</sub>, y P<sub>2</sub>, envían un broadcast con la primera fila de bloques de B hacia cada columna de procesadores. Luego cada procesador realiza la multiplicación local obteniendo un resultado parcial de C correspondiente al primer paso. En el próximo paso, la segunda columna de procesadores, P<sub>1</sub> y P<sub>4</sub>, envían un broadcast de la segunda columna de A hacia cada fila de procesadores, y la segunda fila de procesadores, P<sub>3</sub>, P<sub>4</sub>, y P<sub>5</sub>, realiza un broadcast de la segunda fila de B hacia cada columna de procesadores. Este proceso continúa hasta la última columna de bloques de A y la última fila de bloques de B. En la tabla 2.1 se muestran cada uno de los pasos de SUMMA, detallándose para cada paso, qué envía y qué recibe cada proceso para realizar luego su cálculo local.

| Paso 0            |                    |                                 | in to purpose the | Paso 1             |                                 |  |  |

|-------------------|--------------------|---------------------------------|-------------------|--------------------|---------------------------------|--|--|

| Proceso           | Envía              | Destino                         | Proceso           | Envía              | Destino                         |  |  |

| $P_0$             | col 0 de A         | $P_1, P_2$                      | $P_1$             | col 1 de A         | $P_2, P_0$                      |  |  |

| P <sub>3</sub>    | col 0 de A         | P <sub>4</sub> , P <sub>5</sub> | P <sub>4</sub>    | col 1 de A         | P <sub>5</sub> , P <sub>3</sub> |  |  |

| $P_0$             | fil 0 de <b>B</b>  | P <sub>3</sub>                  | P <sub>3</sub>    | fil 1 de B         | $P_0$                           |  |  |

| $P_1$             | fil 0 de B         | P <sub>4</sub>                  | P <sub>4</sub>    | fil 1 de B         | P <sub>1</sub>                  |  |  |

| P <sub>2</sub>    | fil 0 de <b>B</b>  | P <sub>5</sub>                  | P <sub>5</sub>    | fil 1 de <b>B</b>  | P <sub>2</sub>                  |  |  |

| 144               | Paso 2             | A Designative                   | Paso 3            |                    |                                 |  |  |

| Proceso           | Envia              | Destino                         | Proceso           | Envía              | Destino                         |  |  |

| P <sub>2</sub>    | col 2 de A         | $P_0, P_1$                      | P <sub>0</sub>    | col 3 de A         | $P_1, P_2$                      |  |  |

| P <sub>5</sub>    | col 2 de A         | P <sub>3</sub> , P <sub>4</sub> | P <sub>3</sub>    | col 3 de A         | P <sub>4</sub> , P <sub>5</sub> |  |  |

| $P_0$             | fil 2 de <b>B</b>  | P <sub>3</sub>                  | P <sub>3</sub>    | fil 3 de <b>B</b>  | $P_0$                           |  |  |

| $P_1$             | fil 2 de B         | P <sub>4</sub>                  | P <sub>4</sub>    | fil 3 de B         | P <sub>1</sub>                  |  |  |

| P <sub>2</sub>    | fil 2 de <b>B</b>  | P <sub>5</sub>                  | P <sub>5</sub>    | fil 3 de <b>B</b>  | P <sub>2</sub>                  |  |  |

| Paso 4            |                    |                                 | Paso 5            |                    |                                 |  |  |

| Proceso           | Envía              | Destino                         | Proceso           | Envía              | Destino                         |  |  |

| $P_1$             | col 4 de A         | $P_2, P_0$                      | P <sub>2</sub>    | col 5 de A         | $P_0, P_1$                      |  |  |

| P <sub>4</sub>    | col 4 de A         | P <sub>5</sub> , P <sub>3</sub> | P <sub>5</sub>    | col 5 de A         | P <sub>3</sub> , P <sub>4</sub> |  |  |

| $\overline{P_0}$  | fil 4 de B         | P <sub>3</sub>                  | P <sub>3</sub>    | fil 5 de B         | $P_0$                           |  |  |

| Pi                | fil 4 de B         | P <sub>4</sub>                  | $P_4$             | fil 5 de B         | $P_1$                           |  |  |

| $P_2$             | fil 4 de <b>B</b>  | P <sub>5</sub>                  | P <sub>5</sub>    | fil 5 de <b>B</b>  | P <sub>2</sub>                  |  |  |

|                   | Paso 6             |                                 | Paso 7            |                    |                                 |  |  |

| Proceso           | Envía              | Destino                         | Proceso           | Envía              | Destino                         |  |  |

| $P_0$             | col 6 de A         | $P_1, P_2$                      | P <sub>1</sub>    | col 7 de A         | $P_2, P_0$                      |  |  |

| $P_3$             | col 6 de A         | $P_4, P_5$                      | P <sub>4</sub>    | col 7 de A         | $P_5, P_3$                      |  |  |

| $P_0$             | fil 6 de B         | $P_3$                           | $P_3$             | fil 7 de <b>B</b>  | P <sub>0</sub>                  |  |  |

| $P_1$             | fil 6 de <b>B</b>  | $P_4$                           | P <sub>4</sub>    | fil 7 de B         | $P_{I}$                         |  |  |

| P <sub>2</sub>    | fil 6 de <b>B</b>  | P <sub>5</sub>                  | $P_5$             | fil 7 de <b>B</b>  | P <sub>2</sub>                  |  |  |

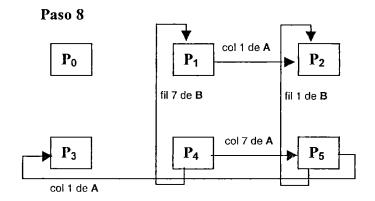

| - 生物 -            | Paso 8             |                                 | A SHIP TOWNE      | Paso 9             | gright en                       |  |  |

| Proceso           | Envía              | Destino                         | Proceso           | Envía              | Destino                         |  |  |

| P <sub>2</sub>    | col 8 de A         | $P_0, P_1$                      | $P_0$             | col 9 de A         | $P_1, P_2$                      |  |  |

| P <sub>5</sub>    | col 8 de A         | P <sub>3</sub> , P <sub>4</sub> | $P_3$             | col 9 de A         | P <sub>4</sub> , P <sub>5</sub> |  |  |

| $P_0$             | fil 8 de B         | P <sub>3</sub>                  | P <sub>3</sub>    | fil 9 de <b>B</b>  | P <sub>0</sub>                  |  |  |

| P <sub>1</sub>    | fil 8 de B         | P <sub>4</sub>                  | $P_4$             | fil 9 de <b>B</b>  | P <sub>1</sub>                  |  |  |

| P <sub>2</sub>    | fil 8 de B         | P <sub>5</sub>                  | P <sub>5</sub>    | fil 9 de <b>B</b>  | P <sub>2</sub>                  |  |  |

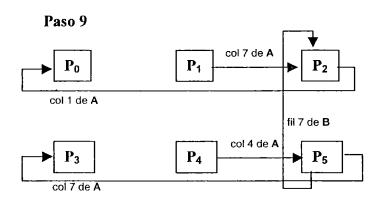

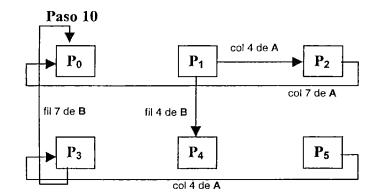

| 4.64              | Paso 10            | PROPER COST MICE                |                   | Paso 11            | 1000                            |  |  |

| Proceso           | Envía              | Destino                         | Proceso           | Envía              | Destino                         |  |  |

| $\frac{P_1}{P_1}$ | col 10 de A        | $P_2, P_0$                      | $P_2$             | col 11 de A        | $P_0, P_1$                      |  |  |

| P <sub>4</sub>    | col 10 de A        | $P_5, P_3$                      | P <sub>5</sub>    | col 11 de A        | $P_3, P_4$                      |  |  |

| $\overline{P_0}$  | fil 10 de <b>B</b> | P <sub>3</sub>                  | $P_3$             | fil 11 de <b>B</b> | P <sub>0</sub>                  |  |  |

| $\frac{P_1}{P_1}$ | fil 10 de <b>B</b> | $P_4$                           | $\frac{1}{P_4}$   | fil 11 de <b>B</b> | P <sub>1</sub>                  |  |  |

| $\overline{P_2}$  | fil 10 de <b>B</b> | $P_5$                           | $P_5$             | fil 11 de <b>B</b> | P <sub>2</sub>                  |  |  |

Tabla 2.1: Pasos en la ejecución del algoritmo SUMMA.

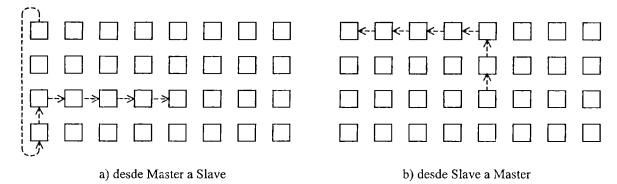

# 4.3.1. Esquema de comunicación de SUMMA

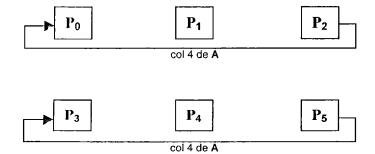

Este algoritmo [Gei95] explota el esquema de comunicación *pipelined*, en donde el broadcast es implementado pasando una columna (o fila) de bloques por todo el anillo lógico que forma la fila (o columna) de procesadores. Por ejemplo, cuando  $P_0$  realiza un broadcast de la primera columna de **A** hacia toda la fila de procesadores, en realidad esta columna es enviada a  $P_1$ , el cual luego la reenviará a  $P_2$  en el próximo paso. En la figura 4.3 se muestra este esquema de comunicación, que posibilita cómputo y comunicación en forma simultánea y eficiente en toda la máquina paralela.

Figura 4.3: Esquema de comunicación pipelined de SUMMA.

# 4.3.2. Tiempo de espera innecesario de SUMMA

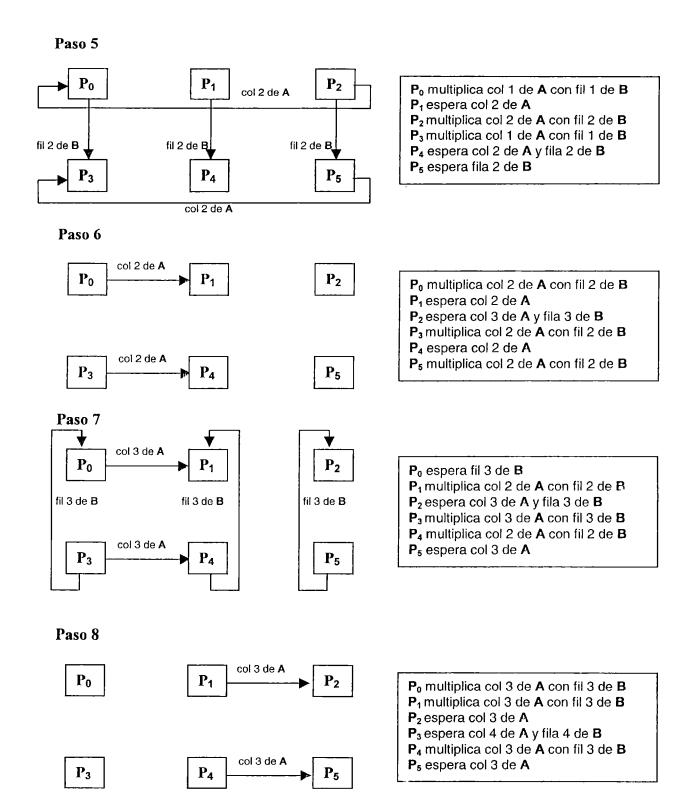

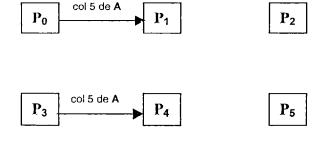

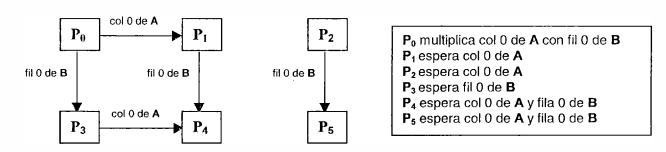

En SUMMA existe un tiempo de espera innecesario que puede mejorarse. Este tiempo de espera se puede observar en el ejemplo anterior: luego de que P<sub>0</sub> multiplica y envía la columna 0 de **A** y la fila 0 de **B**, debe esperar por la columna 1 de **A** (que la tiene P<sub>1</sub>) y la fila 1 de **B** que la tiene P<sub>3</sub>. Cuando P<sub>1</sub> realiza un broadcast de la columna 1 de **A**, por el esquema de comunicación pipelined, se la envía a P<sub>2</sub>, el cual luego se la envía a P<sub>0</sub>. Se puede observar que P<sub>0</sub> tuvo que esperar dos (en realidad Q-1) pasos. Más adelante, cuando P<sub>1</sub> tenga que enviar su próxima columna (4), P<sub>0</sub> (que ya envió la columna 3) tendrá que volver a esperar otros dos pasos, y así para todas sus columnas. En la figura 4.4 se detallan los primeros 13 pasos de la ejecución de SUMMA para el ejemplo anterior. Las flechas entre procesadores indican el envío de datos, y para cada paso se puede observar el estado de cada procesador, si esta calculando o esperando. Si se sigue cuidadosamente esta figura se puede notar que cada procesador, luego de enviar sus datos, debe esperar al menos dos pasos para poder recibir la siguiente columna de **A** y fila de **B** para realizar la multiplicación.

col 1 de A

# Paso 9

Po espera col 4 de A

P<sub>1</sub> multiplica col 4 de A con fil 4 de B

P<sub>2</sub> multiplica col 3 de A con fil 3 de B

P<sub>3</sub> espera col 4 de A y fila 4 de B

P<sub>4</sub> espera fila 4 de B

P<sub>5</sub> multiplica col 3 de A con fil 3 de B

Paso 10

Po espera coi 4 de A

P<sub>1</sub> espera col 5 de A y fila 5 de B

P<sub>2</sub> multiplica col 4 de A con fil 4 de B

P<sub>3</sub> espera col 4 de A

P<sub>4</sub> multiplica col 4 de A con fil 4 de B

P<sub>5</sub> multiplica col 4 de A con fil 4 de B

Po multiplica col 4 de A con fil 4 de B

P<sub>1</sub> espera col 5 de A y fila 5 de B

P<sub>2</sub> espera fil 5 de B

P<sub>3</sub> multiplica col 4 de A con fil 4 de B

P<sub>4</sub> espera col 5 de A

P<sub>5</sub> multiplica col 5 de A con fil 5 de B

# Paso 12

Po multiplica col 5 de A con fil 5 de B

P<sub>1</sub> espera col 5 de A

P<sub>2</sub> multiplica col 5 de A con fil 5 de B

P<sub>3</sub> multiplica col 5 de A con fil 5 de B

P<sub>4</sub> espera col 5 de A

P<sub>5</sub> espera col 6 de A con fil 6 de B

# Paso 13

Figura 4.4: Pasos intervientes en la comunicación pipelined de SUMMA.

# 4.4. DIMMA

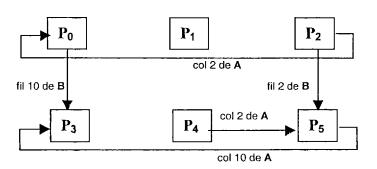

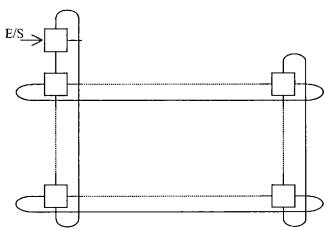

DIMMA implementa la multiplicación de matrices en forma rápida y escalable con distribución de datos cíclica sobre computadoras concurrentes con memoria distribuida. Este nuevo algoritmo se basa en el algoritmo SUMMA [Gei95], al que le incorpora dos nuevas ideas. Por un lado utiliza un "esquema de comunicación pipelined modificado", que hace que el algoritmo sea eficiente al superponer comunicación y cómputo en forma efectiva. Además utiliza el concepto del mínimo común múltiplo LCM detallado más adelante.

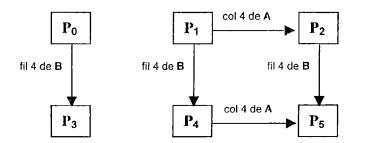

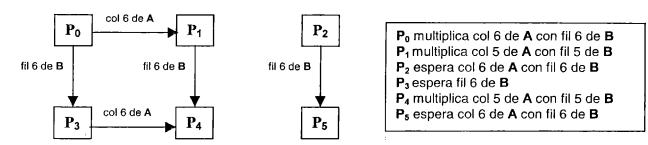

# 4.4.1. Esquema de comunicación de DIMMA

DIMMA modifica el esquema de comunicación de SUMMA de la siguiente manera: cada procesador realiza un broadcast de todas las columnas de A y filas de B que tiene a los demás procesadores antes de que el próximo procesador comience a realizar un broadcast de sus datos.

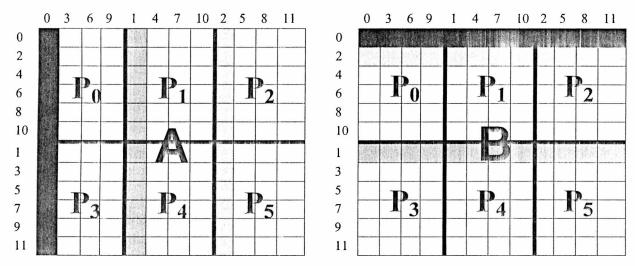

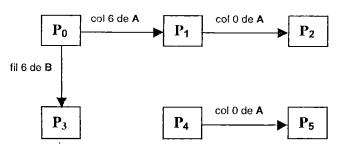

Con este nuevo esquema, DIMMA se implementa de la siguiente manera. Sea  $L_m$  el número de columna de bloques de  $\bf A$  y fila de bloques de  $\bf B$  correspondiente al paso actual. En el primer paso,  $L_m=0$ , se envía un broadcast y multiplica la columna  $L_m$  de  $\bf A$  y la fila  $L_m$  de  $\bf B$ . En el próximo paso,  $L_m$  tendrá valor 6, por lo cual la primera columna de procesadores,  $P_0$  y  $P_3$ , realiza un broadcast de la columna número 6 de  $\bf A$  hacia cada fila de procesadores; y la primera fila de procesadores,  $P_0$ ,  $P_1$ , y  $P_2$ , envían la fila 6 de  $\bf B$  hacia cada columna de procesadores, como se muestra en la figura 4.5. El valor 6 se debe a que es el mínimo común múltiplo (LCM) de  $\bf P=2$  y  $\bf Q=3$ , y se utiliza porque los bloques a distancia LCM, en filas y columnas, siempre se encontrarán en el mismo procesador por la forma de distribución cíclica. En cambio, en el algoritmo SUMMA, en el segundo paso,  $L_m$  sería igual a 1, por lo que los procesadores  $\bf P_1$  y  $\bf P_4$  enviarían la columna 1 de  $\bf A$  y los procesadores  $\bf P_3$ ,  $\bf P_4$ ,  $\bf P_5$  enviarían la columna de  $\bf B$ , produciéndose las esperas antedichas.

Figura 4.5: Algoritmo DIMMA. Los bloques más obscuros son enviados primero y los más claros después.

En el tercer y cuarto paso,  $L_m$  tendrá los valores 3 y 9 respectivamente, por lo cual la primera columna de procesadores,  $P_0$  y  $P_3$ , envían hacia todas la filas, de las columna 3 y 9 de A, y la segunda fila de procesadores,  $P_3$ ,  $P_4$ , y  $P_5$ , envían un broadcast hacia todas la columnas, de las filas 3 y 9 de B, respectivamente.

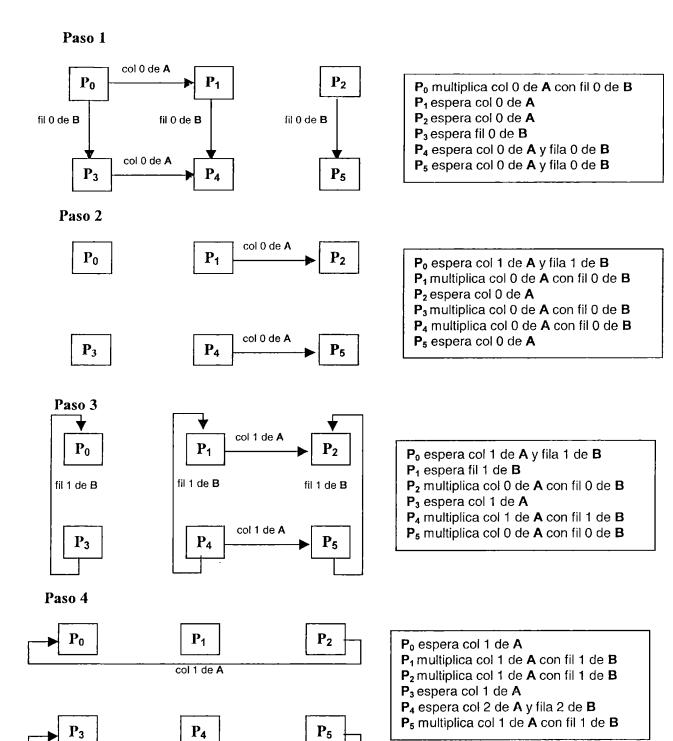

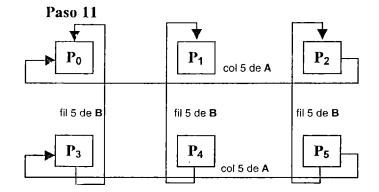

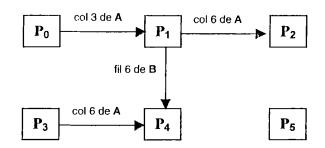

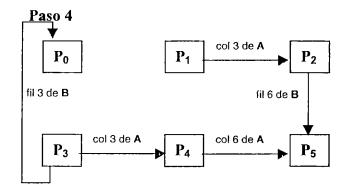

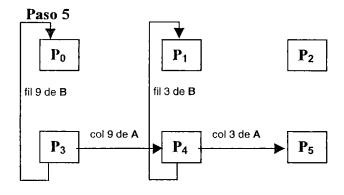

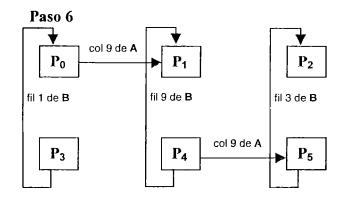

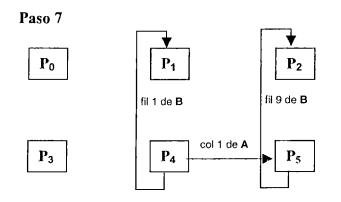

Este nuevo esquema de comunicación introducido por DIMMA elimina el tiempo de espera innecesario que existe en SUMMA. Esto lo realiza al enviar cada procesador todas sus columnas y filas en forma consecutiva, de esta manera el tiempo de espera de SUMMA aparecerá sólo cuando cada procesador termine de enviar todos sus datos y debe esperar por los del siguiente procesador. En el caso de SUMMA este tiempo aparece por cada  $L_m$ , ya que éste  $L_m$  se recorre en forma consecutiva y los  $L_m$  consecutivos pertenecen a distintos procesadores, tanto en columnas y filas de A y B (ver distribución cíclica). En la Figura 4.6, se muestran los primeros 13 pasos de la comunicación pipelined de DIMMA.

## Paso 1

#### Paso 2

$P_0$  multiplica col 6 de  ${f A}$  con fil 6 de  ${f B}$

P<sub>1</sub> multiplica col 0 de A con fil 0 de B

P2 espera col 0 de A

P<sub>3</sub> multiplica col 0 de A con fil 0 de B

P<sub>4</sub> multiplica col 0 de A con fil 0 de B

P<sub>5</sub> espera col 0 de A

#### Paso 3

Po espera fil 3 de B

P<sub>1</sub> multiplica col 6 de A con fil 6 de B

P<sub>2</sub> multiplica col 0 de A con fil 0 de B

P<sub>3</sub> multiplica col 6 de A con fil 6 de B

P4 espera col 6 de A y fil 6 de B

P<sub>5</sub> multiplica col 0 de A con fil 0 de B

Po espera fil 3 de B

P<sub>1</sub> espera fil 3 de B

P<sub>2</sub> multiplica col 6 de A con fil 6 de B

P<sub>3</sub> multiplica col 3 de A con fil 3 de B

P<sub>4</sub> multiplica col 6 de A con fil 6 de B

P<sub>5</sub> espera col 6 de A y fil 6 de B

Po multiplica col 3 de A con fil 3 de B

P<sub>1</sub> espera fil 3 de B

P<sub>2</sub> espera fil 3 de B

P<sub>3</sub> multiplica col 9 de A con fil 9 de B

P<sub>4</sub> multiplica col 3 de A con fil 3 de B

P<sub>5</sub> multiplica col 6 de A con fil 6 de B

$P_0$  multiplica col 9 de  ${f A}$  con fil 9 de  ${f B}$

P<sub>1</sub> multiplica col 3 de A con fil 3 de B

P2 espera fila 3 de B

P<sub>3</sub> espera col 1 de A

$P_4$  multiplica col 9 de  ${f A}$  con fil 9 de  ${f B}$

P<sub>5</sub> multiplica col 3 de A con fil 3 de B

Po espera col 1 de A

P<sub>1</sub> multiplica col 9 de A con fil 9 de B

P<sub>2</sub> multiplica col 3 de A con fil 3 de B

P<sub>3</sub> espera col 1 de A

P<sub>4</sub> multiplica col 1 de A con fil 1 de B

P<sub>5</sub> multiplica col 9 de A con fil 9 de B

Po espera col 1 de A

P<sub>1</sub> multiplica col 1 de A con fil 1 de B

P<sub>2</sub> multiplica col 9 de A con fil 9 de B

P<sub>3</sub> espera col 1 de A

P<sub>4</sub> multiplica col 7 de A con fil 7 de B

P<sub>5</sub> multiplica col 1 de A con fil 1 de B

Po espera col 1 de A

P<sub>1</sub> multiplica col 7 de A con fil 7 de B

P<sub>2</sub> multiplica col 1 de A con fil 1 de B

P<sub>3</sub> multiplica col 1 de A con fil 1 de B

P<sub>4</sub> espera fila 4 de B

P<sub>5</sub> multiplica col 7 de A con fil 7 de B

P<sub>0</sub> multiplica col 1 de A con fil 1 de B

P<sub>1</sub> multiplica col 4 de A con fil 4 de B

P<sub>2</sub> multiplica col 7 de A con fil 7 de B

P<sub>3</sub> multiplica col 7 de A con fil 7 de B

P<sub>4</sub> espera fila 4 de B

P<sub>5</sub> espera fila 4 de B

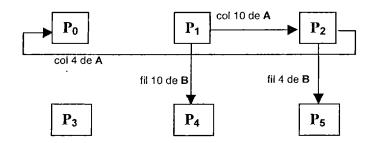

#### Paso 11

P<sub>0</sub> multiplica col 7 de A con fil 7 de B

P<sub>1</sub> espera col 10 de A y fila 10 de B

P<sub>2</sub> multiplica col 4 de A con fil 4 de B

P<sub>3</sub> espera fil 4 de B

P<sub>4</sub> multiplica col 4 de A con fil 4 de B

P<sub>5</sub> espera fila 4 de B

#### Paso 12

P<sub>0</sub> multiplica col 4 de A con fil 4 de B

P<sub>1</sub> espera col 2 de A

P<sub>2</sub> multiplica col 10 de A con fil 10 de B

P<sub>3</sub> espera fil 4 de B

P<sub>4</sub> multiplica col 10 de A con fil 10 de B

P<sub>5</sub> multiplica col 4 de A con fil 4 de B

#### Paso 13

P<sub>0</sub> multiplica col 10 de A con fil 10 de B

P<sub>1</sub> espera col 2 de A

P<sub>2</sub> multiplica col 2 de A con fil 2 de B

P<sub>3</sub> multiplica col 4 de A con fil 4 de B

P<sub>4</sub> multiplica col 2 de A con fil 2 de B

P<sub>5</sub> multiplica col 10 de A con fil 10 de B

Figura 4.6: Pasos intervientes en la comunicación pipelined de DIMMA.

## 4.4.2. Concepto de LCM

DIMMA incorpora el concepto de LCM. Nos referiremos a un cuadrado de LCMxLCM bloques como un bloque LCM. La matriz de la figura 4.3 puede ser vista como una matriz de 2x2 de LCM bloques. Un algoritmo paralelo, el cual el orden de ejecución puede ser entremezclarse la multiplicación de matrices y transposición de matrices, puede ser desarrollado para el primer bloque LCM. Entonces puede ser directamente aplicado a los demás bloques LCM, los cuales tienen la misma estructura y la misma distribución que el primer bloque LCM, esto es, cuando una operación es ejecutada en el primer bloque LCM, la misma operación puede ser realizada simultáneamente en los otros bloques LCM [Choi].