# Consumo energético de sistemas de Computación de Altas Prestaciones

Javier Balladini, Marina Morán, Claudia Rozas, Armando De Giusti<sup>1</sup>, Remo Suppi<sup>2</sup>, Dolores Rexachs<sup>2</sup>, Emilio Luque<sup>2</sup>

Facultad de Informática, Universidad Nacional del Comahue

Buenos Aires 1400, Neuquén Capital, Tel. +54 299 4490300

{javier.balladini, marina, claudia.rozas}@fi.uncoma.edu.ar

Instituto de Investigación en Informática LIDI, Universidad Nacional de La Plata

50 y 120 - 2do Piso, La Plata, Tel. +54 221 4227707

degiusti@lidi.info.unlp.edu.ar

<sup>2</sup> Departamento de Arquitectura de Computadores y Sistemas Operativos, Universidad Autónoma de Barcelona Campus UAB, Edifici Q, 08193 Bellaterra (Barcelona), España. Tel: +34 93 581 1990 {remo.suppi, dolores.rexachs, emilio.luque}@uab.es

### Resumen

En la última década, el consumo energético ha dirigido el diseño de todos los sistemas de cómputo, desde dispositivos móviles a los cuales cada vez se le piden más prestaciones que deben ser soportadas por una pequeña batería, hasta los sistemas de Cómputo de Altas Prestaciones (HPC, de High Performance Computing), objeto de nuestro interés, los cuales consumen enormes cantidades de energía. Esta alta demanda energética tiene serias consecuencias financieras, medioambientales, y en muchos casos también sociales. El aumento de la eficiencia energética de los sistemas de HPC no solo proviene de las nuevas arquitecturas hardware, también está involucrado el software, quien debe gestionar y configurar el sistema para mantener un determinado equilibrio entre tiempo de ejecución, eficiencia energética y productividad.

Esta situación nos ha motivado a realizar una colaboración entre tres universidades para estudiar diferentes temas relacionados a la computación ecológica. Nuestro trabajo se centra en el desarrollo de software para sistemas de HPC que permita gestionar su consumo energético al ejecutar aplicaciones paralelas.

Palabras claves: computación ecológica, eficiencia energética, computación de altas prestaciones

### 1. Contexto

La investigación aquí presentada surge como una colaboración entre la Facultad de Informática de la Universidad Nacional del Comahue (UNCOMA), el Instituto de Investigación en Informática LIDI de la Universidad Nacional de La Plata (UNLP), y el grupo de investigación HPC4EAS (High Performance Computing for Efficient Applications and Simulation) de la Universidad Autónoma de Barcelona (España). La colaboración se centra en el estudio del consumo energético de los sistemas de cómputo paralelo al ejecutar aplicaciones científicas computacionalmente complejas.

La financiación de las líneas de investigación aquí presentadas provienen del proyecto de investigación de UNCOMA "04/F004: Informática Aplicada al Medio Académico y Científico" y el Inter-U "Colaboración UNComa-UNLP: docencia e investigación en Sistemas Paralelos" de PROMINF, y de otros proyectos de la UNLP y del grupo HPC4EAS.

#### 2. Introducción

Los sistemas de Cómputo de Altas Prestaciones (HPC, de High Performance Computing) han tenido, por décadas, el único objetivo de incrementar la velocidad de procesamiento de las aplicaciones científicas de alta demanda computacional. Esto se ve reflejado en la lista del TOP500 [2], que utiliza la métrica FLOPS (FLoating-point OPerations per Second, cantidad de operaciones de coma flotante por segundo) para determinar el orden de clasificación de las supercomputadoras. Sólo importaban las prestaciones y, principalmente para el dueño de la supercomputadora, la relación precio/prestaciones. Así, las supercomputadoras se volvieron tan grandes que llegan a consumir tan-

ta electricidad como una ciudad¹ impactando fuertemente en lo económico (y posiblemente en lo ecológico y social²), no solo por su consumo energético específico sino también por la energía requerida para refrigerar el sistema (que puede llegar a demandar tanto como el propio sistema de cómputo) y así asegurar su correcto funcionamiento.

El consumo energético, un factor limitante para el HPC [12], ha dado lugar a la nueva era de la supercomputación ecológica. Podríamos decir que el gran hito que determinó esta nueva era data de 2007. En ese año, una nueva entidad denominada Green500 [1], surgida como alternativa o complemento del TOP500, publica su primera lista que clasifica a las supercomputadoras de mayor eficiencia energética del mundo; esta clasificación considera el rendimiento por W (FLOPS/W) de cada supercomputadora al ejecutar un cierto benchmark. La eficiencia energética de los sistemas está mejorando drásticamente, no obstante, como las mismas continuan incrementando su tamaño, su consumo energético sigue en aumento. Sin considerar el sistema de refrigeración, la actual supercomputadora más rápida del mundo demanda 17 MW de potencia, más que ninguna otra en la historia de la computación, significando un costo anual de aproximadamente 17 millones de dólares.

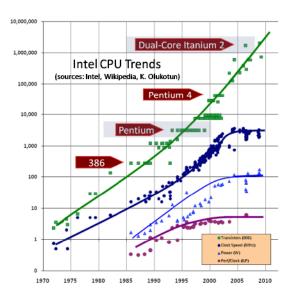

El consumo energético está dirigiendo el diseño de todos los sistemas de computación, y no solo de los sistemas de HPC. La revolución de los dispositivos móviles (notebooks, smartphones, tablets) ha sido uno de los principales motivadores, de cuyos dispositivos cada vez se espera que realicen más procesamiento con iguales capacidades energéticas que obtienen de sus pequeñas baterías. Los procesadores han sufrido drásticos cambios al considerarse la eficiencia energética en el diseño de los mismos. En la figura 1 es posible observar la evolución de ciertos parámetros. Hasta el año 2005 no solo se ha doblado el número de transistores cada 18-24 meses para incrementar las prestaciones de los procesadores (ley de Moore), sino que también se ha doblado el consumo energético[11]. A partir del 2005 el número de transistores continuó

Figura 1: Evolución de los procesadores. Fuente: Intel

| Model Number | Cores | Frequency | L2 cache   | L3 cache | TDP   | Socket   | I/O bus          |

|--------------|-------|-----------|------------|----------|-------|----------|------------------|

| Xeon E5-4640 | 8     | 2.4 GHz   | 8 × 256 KB | 20 MB    | 95 W  | LGA 2011 | 2 × 8.0 GT/s QPI |

| Xeon E5-4650 | 8     | 2.7 GHz   | 8 × 256 KB | 20 MB    | 130 W | LGA 2011 | 2 × 8.0 GT/s QPI |

Cuadro 1: Características de procesadores Sandy Bridge-EP

incrementándose, pero el consumo energético se mantuvo constante. Este logro está basado en el desarrollo de procesadores con múltiples cores (nucleos) que trabajan a una menor frecuencia de reloj (menor cantidad de ciclos de reloj por unidad de tiempo). A modo de ejemplo, en el cuadro 1 se muestra una tabla comparativa de la línea de procesadores de Intel para servidores "Sandy Bridge-EP" (32 nm) Efficient Performance. Se puede observar la influencia de la velocidad del procesador en la potencia energética demandada, en tal caso, el Xeon E5-4650 tiene una frecuencia de reloj un 12,5% mayor a la del Xeon E5-4640 pero demanda un 36,8% más de potencia eléctrica<sup>3</sup>.

Además de la explotación de paralelismo a través de múltiples cores, hay otros técnicas que permiten mejorar la eficiencia energética de los procesadores. Es importante mencionar que estas técnicas involucran en ciertos casos tanto al hardware como al software [7], y entre las más importantes se encuentran:

- Nivel de circuito y lógico [17]: involucra tecnología de dispositivos (transistores) y reordenamiento de puertas lógicas.

- 2. Interconexión de unidades funcionales y no-

<sup>&</sup>lt;sup>1</sup>En 2002, el Dr. Eric Schmidt, CEO de Google, dijo "lo que más importa a los diseñadores de computadoras de Google no es la velocidad sino el consumo energético, porque los centros de datos pueden consumir tanta electricidad como una ciudad" [13].

<sup>&</sup>lt;sup>2</sup>La falta de explotación de las energías renovables y limpias hacen que la producción energética afecte en lo ecológico y social. La mayor cantidad (y más grandes) de las supercomputadoras del mundo están en EEUU, donde la mitad de la energía eléctrica en éste país se produce con carbón [3], impactando fuertemente en el medio ambiente, y la salud y riesgo de vida de las personas, por causa de la extracción del mineral y la contaminación por combustión del carbón, entre otros.

<sup>&</sup>lt;sup>3</sup>La métrica utilizada en la tabla comparativa se denomina Thermal Design Power (TDP), que representa la máxima potencia que un sistema de refrigeración requiere disipar al ejecutar una "aplicación real".

- dos: involucra rediseño de buses y redes de interconexión.

- Optimizaciones de memoria: jerarquía de memoria.

- 4. Arquitecturas adaptables e hibernación de recursos [9]: involucran cachés de activación parcial, discos, cores, unidades funcionales, tarjetas de interfaz de red, memorias.

- 5. Integración on-chip.

- Procesadores de propósito especial: uso de Unidades de Procesamiento Gráfico (GPUs).

- 7. Rediseño de algoritmos de aplicaciones.

- 8. Planificación de tareas y asignación de tareas a recursos hardware [5].

- Escalado dinámico de frecuencia y tensión [16].

### 3. Línea de investigación

Nuestro trabajo no pretende desarrollar nuevas tecnologías hardware que tengan una mayor eficiencia energética (diseño ecológico [14]), sino gestionar mediante software el hardware existente para reducir el consumo energético (uso ecológico [14]). Nos centramos en el desarrollo de metodologías, modelos y construcción de software para administrar y gestionar el consumo de energía y prestaciones.

Nuestra investigación se enfoca en las siguientes temáticas energéticas aplicadas a sistemas de computación de altas prestaciones:

- Caracterización energética de los sistemas. La caracterización energética puede ser utilizada para comparar sistemas, para conocer el comportamiento energético del sistema bajo estudio y así diseñar aplicaciones con conocimiento de la energía, y ser un soporte para la construcción de modelos de predicción de energía y potencia. Nos interesan plataformas basadas en CPUs (Central Processing Unit) y GPUs (Graphics Processing Unit).

- 2. Predicción de energía y rendimiento. Es importante proveer a un administrador de sistema de herramientas que permitan predecir la energía y el rendimiento que producirían distintas configuraciones del sistema al ejecutar una dada aplicación paralela, y así poder seleccionar la configuración adecuada que mantenga el compromiso deseado entre tiempo de ejecución y eficiencia energética.

- 3. Predicción de potencia. La predicción de la potencia es necesaria debido a que, en general, los sistemas no disponen de dispositivos internos de medición, en tiempo real, de la potencia demandada; dispositivos externos son imprácticos para sistemas con gran número de nodos y procesadores por nodo. El objetivo de la predicción de potencia es permitir el desarrollo de algoritmos DVFS (ver siguiente punto) que no podrían ser propuestos sin esta información.

- 4. Diseño de algoritmos de escalado dinámico de frecuencia y tensión (DVFS, Dynamic Voltage and Frequency Scaling). La reducción de la tensión suministrada a un circuito reduce el consumo energético, sin embargo, incrementa el retardo de las compuertas lógicas que fuerza a reducir la frecuencia de reloj para que el circuito continúe trabajando correctamente. Basándose en este concepto, los algoritmos DVFS intentan reducir el consumo energético realizando cambios dinámicos de la frecuencia de reloj de los cores.

- 5. Estrategias energéticas en cloud computing. El cloud computing es un paradigma, relativamente nuevo, de cómputo distribuido que se presenta como una evolución natural del concepto de clusters y grids. Proporciona grandes conjuntos de recursos virtuales (hardware, plataformas de desarrollo, almacenamiento y/o aplicaciones), fácilmente accesibles. Considerando sus grandes dimensiones, y la tendencia natural a que la plataforma escale para ampliar los servicios provistos, nos interesa estudiar las posibles alternativas que permitan reducir su alta demanda energética.

- 6. Gestión energética en mecanismos de tolerancia a fallos. La tolerancia a fallos agrega una carga de trabajo significativa al sistema de cómputo, sobre todo en sistemas que tienen enormes cantidades de unidades de procesamiento, haciendo necesario gestionar el consumo energético de los distintos mecanismos.

## 4. Resultados y objetivos

En referencia a la temática de caracterización energética de los sistemas, se ha estudiado la influencia de los modelos de programación paralela (OpenMP y MPI) y escalado de frecuencias de CPUs en sistemas de computación de altas prestaciones de memoria compartida [7]. También hemos estudiado los factores influyentes en el

consumo energético de los sistemas de cómputo de altas prestaciones basados en CPUs y GPUs [8]. Posteriormente, hemos propuesto una metodología para caracterizar la potencia de sistemas de computación de altas prestaciones de memoria compartida [6]. La metodología involucra la búsqueda de factores influyentes en la potencia del sistema, realizando un análisis de sensibilidad de las propiedades de la carga de trabajo y parámetros del sistema en el comportamiento de potencia. La carga de trabajo considera aspectos de cómputo y comunicaciones de las aplicaciones. Esta metodología es similar a trabajos previos, pero nosotros proponemos un esquema de mayor profundidad que puede ayudar a mejorar la caracterización del sistema. También realizamos estudios sobre el impacto del sistema de Entrada/Salida en la eficiencia energética, que publicamos en [15].

En relación al diseño de algoritmos DVFS, hemos propuesto un algoritmo de mejora de la eficiencia energética para sistemas de memoria compartida [10], basado en la aceleración de los relojes de los cores en momentos de bajo paralelismo.

Respecto a la predicción de energía y estrategias energéticas en cloud computing, hemos propuesto una metodología para predecir el consumo energético de aplicaciones SPMD en entornos virtualizados, que publicamos en [5]. La metodología se basa en el desarrollo de un modelo analítico para predecir el consumo de energía y el producto energía-tiempo (EDP, Energy Delay Product). Las consideran aplicaciones SPMD diseñadas con la librería de paso de mensajes (MPI, Message Passing Interface), gran volúmen de comunicación, que pueden generar problemas de balances de carga que afectan seriamente el tiempo de ejecución y la eficiencia energética. El método fue validado usando aplicaciones científicas y se observó una precisión de predicción entre el 91 y 96 %.

Los métodos de tolerancia a fallos tienen fuerte incidencia en el consumo energético de los sistemas de HPC, y resulta de suma importancia conocer, antes de ejecutar una cierta aplicación, el impacto que pueden producir los diferentes métodos y configuraciones del mismo. En [4], presentamos una metodología para predecir el consumo energético producido por el método de checkpoint coordinado remoto. La metodología se basa en una caracterización energética del sistema, una caracterización de la aplicación, y un modelo analítico que se instancia con los parámetros caracterizados. El modelo permite predecir la energía que consumirán los checkpoints para cualquier tamaño de problema y frecuencia de CPU de ejecución de checkpoints. Los resultados de las predicciones muestran una precisión mayor al 95 %.

Actualmente nuestros principales objetivos están orientados a:

- Determinar el impacto en el consumo energético no solo los fallos sino también sus recuperaciones.

- Proponer mecanismos de gestión de tolerancia a fallos que procuren un uso eficiente del cluster, permitiendo maximizar la productividad y minimizar el consumo energético.

- Validar la metodología propuesta de predicción del consumo energético de aplicaciones SPMD.

- Continuar los estudios de predicción de potencia.

# 5. Formación de recursos humanos

Los estudios aquí expuestos tienen como objetivo formar recursos humanos a nivel de grado y postgrado. En la Universidad Nacional del Comahue, hemos presentado una tesis de Licenciatura en Ciencias de la Computación en el tema de "Computación de Altas Prestaciones Ecológica con GPUs", y se está finalizando otra en el tema "Algoritmos de mejora de la eficiencia energética para sistemas de memoria compartida". Estamos trabajando en la definición de una propuesta de tesis doctoral relacionada a mecanismos de tolerancia a fallos con conocimiento de la energía.

### Referencias

- $\label{eq:constraint} \textbf{[2]} \ \ \textbf{Sitio web del top} \ \textbf{500:} \ \ \textbf{http://www.top} \ \textbf{500.org/}.$

- $[3] \begin{tabular}{ll} U.s. & geological & survey, \\ & http://energy.usgs.gov/coal.html. \end{tabular}$

- [4] Javier Balladini, Marina Morán, Dolores Rexachs, and Emilio Luque. Metodología para predecir el consumo energético de checkpoints en sistemas de hpc. XX Congreso Argentino de Ciencias de la Computación (CACIC 2014), 2014.

- [5] Javier Balladini, Ronal Muresano, Remo Suppi, Dolores Rexachs, and Emilio Luque. Methodology for predicting the energy consumption of spmd application on virtualized environments. Computer Science and Technology (JCST), 13(3):130-136, 2013.

- [6] Javier Balladini, Enzo Rucci, Armando Eduardo De Giusti, Marcelo Naiouf, Remo Suppi, Dolores Rexachs del Rosario, and Emilio Luque Fadón. Power characterisation of shared-memory hpc systems. In XVIII Congreso Argentino de Ciencias de la Computación, 2012.

- [7] Javier Balladini, Remo Suppi, Dolores Rexachs, and Emilio Luque. Impact of parallel programming models and cpus clock frequency on energy consumption of hpc systems. Computer Systems and Applications, ACS/IEEE International Conference on, 0:16-21, 2011.

- [8] Javier Balladini, Federico Uribe, Remo Suppi, Dolores Rexachs, and Emilio Luque. Factores influyentes en el consumo energético de los sistemas de computación de altas prestaciones basados en cpus y gpus. XVII Congreso Argentino de Ciencias de la Computación (CACIC 2011), pages 271-281, 2011.

- [9] Domingo Benitez, Juan C. Moure, Dolores Rexachs, and Emilio Luque. A reconfigurable cache memory with heterogeneous banks. In Proceedings of the Conference on Design, Automation and Test in Europe, DATE '10, pages 825–830, 3001 Leuven, Belgium, Belgium, 2010. European Design and Automation Association.

- [10] Belén Casanova, Javier Balladini, Armando Eduardo De Giusti, Remo Suppi, Dolores Rexachs del Rosario, and Emilio Luque Fadón. Mejora de la eficiencia energética en sistemas de computación de altas prestaciones. In XVIII Congreso Argentino de Ciencias de la Computación, 2012.

- [11] Wu-Chun Feng. The importance of being low power in high-performance computing. Cyberinfrastructure Technology Watch Quarterly (CTWatch Quarterly), 1(3):11-20, August 2005.

- [12] Wu-Chun Feng, Xizhou Feng, and Rong Ge. Green supercomputing comes of age. IT Professional, 10(1), January 2008.

- [13] John Markoff and Steve Lohr. Intel's huge bet turns iffy. New York Times, September 29, 2002.

- [14] San Murugesan. Harnessing green it: Principles and practices. IT Professional, 10:24-33, January 2008.

- [15] Javier Panadero, Sandra Méndez, Dolores Rexachs, Javier Balladini, Ismael Rodriguez, Adrián Pousa, Remo Suppi, and Emilio Luque. El impacto del sistema de entrada/salida en la eficiencia energética. In XVII Congreso Argentino de Ciencias de la Computación, 2011.

- [16] Barry Rountree, David K. Lownenthal, Bronis R. de Supinski, Martin Schulz, Vincent W. Freeh, and Tyler Bletsch. Adagio: making dvs practical for complex hpc applications. In ICS '09: Proceedings of the 23rd international conference on Supercomputing, pages 460–469, New York, NY, USA, 2009. ACM.

[17] Vasanth Venkatachalam and Michael Franz. Power reduction techniques for microprocessor systems. ACM Computing Surveys, 237:2005, 2005