# ANÁLISIS, SIMULACIÓN E IMPLEMENTACIÓN DE LA ETAPA DE POTENCIA DE UN INVERSOR MONOFÁSICO CONECTADO A RED

## V. Serrano, Hoyos D., Villena M.

Instituto de Investigación en Energías No Convencionales (INENCO) Consejo de Investigación Universidad Nacional de Salta (CIUNSA) Avenida Bolivia 5150 C.P. 4400 – Salta Tel. 03874255578 – email: vserranohugo@gmail.com

Recibido 18/08/14, aceptado 29/09/14

**RESUMEN:** Este trabajo tiene como objetivo el análisis de la etapa de potencia del inversor, utilizar una herramienta de simulación para corroborar su funcionamiento y como meta armar un prototipo en el laboratorio comparando los resultados con los simulados. Se espera también, aprender sobre nuevas tecnologías utilizadas en la electrónica de potencia. Primero se estudió el estado del arte de los inversores para conexión a red, se seleccionó una topología que podía ser replicada en el laboratorio y a posterior se procedió a realizar el montaje del mismo. Como resultado se obtuvo una señal senoidal de bajo desempeño, como conclusión se valora el conocimiento adquirido en el manejo de nuevos componentes electrónicos y se propone mejorar los resultados obtenidos y profundizar en la investigación sobre nuevas tecnologías.

Palabras clave: Inversor foto-voltaico con conexión a red, simulación, puente H.

#### INTRODUCCION

En la actualidad, a nivel mundial se observa una mayor demanda de energía, especialmente por electricidad. Una causa que se destaca de esta situación es el aumento en la cantidad de habitantes a nivel mundial. Los mismos alcanzan un mayor poder adquisitivo que demandan más servicios y confort. (Crossette, 2011). Esta realidad promociona una expansión en las industrias y en un mayor uso de los medios de transportes, tanto públicos como privados. El funcionamiento de estos servicios se hace posible utilizando combustibles fósiles; como son el gas, carbón y petróleo, el uso masivo de estos productos trae como consecuencia elevados niveles de contaminación que afectan al medio ambiente y además su producción no es sostenible en el tiempo, porque son recursos energéticos no renovables.

En este contexto energético mundial, el uso de la energía solar (FV – Foto-Voltaica) se ha expandido en los últimos años gracias a las promociones de distintos gobiernos para la utilización de las energías renovables,(Renac, 2011) especialmente en países europeos que se impusieron como meta disminuir el consumo de energía proveniente de fuentes que se van extinguiendo y a la vez producen grandes niveles de contaminación a escala global. Una de las aplicaciones que más desarrollo tuvieron, y aún hoy continúan, es la generación de electricidad a partir de generadores FV conectados a la red eléctrica. Se emplazan en lugares cercanos a las redes de distribución creando sistemas de (GD - Generación Distribuida). En los países en donde el desarrollo de este tipo de emprendimientos es sostenido, se instalan granjas solares en la vecindad de pequeñas ciudades o bien se utilizan las fachadas de edificios públicos, privados o comerciales. También se usan los techos de casas particulares para su instalación.(Mérida et al., 2010).

En nuestro país y particularmente en la provincia de Salta, esta clase de emprendimientos se encuentran en etapas de laboratorios o comenzando a ensayar con inversores de baja potencia, como la minicentral fotovoltaica conectada a red en el predio de la Universidad Nacional de Salta, con un potencia de 600W (Javi et al., 2012), también se encuentra en funcionamiento instalaciones en edificios públicos, como es el proyecto IRESUD, que en nuestra provincia se montó en la Escuela de la Magistratura del Poder Judicial de Salta, con una potencia de 2800W. (Javi et al., 2013).

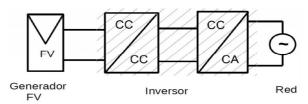

Los sistemas fotovoltaicos de GD están formados por: (i) Generador FV que es un conjunto de paneles asociados de tal manera que se pueda extraer la mayor cantidad de energía posible, (ii) El inversor, que es un dispositivo electrónico que se encarga de transferir la energía eléctrica de los paneles hacia la red, previa adaptación en tensión, fase, frecuencia y además debe poseer circuitos de seguridad. (iii) La red eléctrica. Figura 1.

Figura 1. Sistema de Generación Distribuida FV.

Los inversores presentan un continuo desarrollo en la mejora de su eficiencia, esto se debe a los nuevos componentes que forman parte de la electrónica de potencia y a los avances en investigación para encontrar o mejorar códigos que permiten aprovechar al máximo la energía que entregan los generadores FV, también realizan su contribución las nuevas lógicas de control que hacen funcionar a los elementos de conmutación con muy poca pérdida de energía por calentamiento.

La etapa de potencia del inversor se puede clasificar en dos tipos de topologías: (i) con aislación galvánica y (ii) sin aislación galvánica. (Kjaer et al, 2005) En la primera, el inversor puede estar constituido por dos etapas, la etapa (CC-CC, Corriente Continua-Corriente Continua) en donde la aislación se obtiene con un transformador de alta frecuencia que es el encargado de elevar la tensión del generador FV y en el segundo caso, la etapa de potencia (CC-CA, Corriente Continua-Corriente Alterna) el transformador que provee la aislación trabaja a la misma frecuencia de la red teniendo como desventaja el excesivo peso y su gran volumen. Para cualquiera de las dos situaciones se obtiene la ventaja de la aislación, pero, a costa de obtener una eficiencia menor debido a las pérdidas de energía que se desarrollan en el transformador.

Los avances en la eficiencia se logra en las topologías sin aislación galvánica o también denominada sin transformador o transformer-less, las más destacadas son: Puente completo, medio puente, (NPC - Neutral Point Clamp), (HERIC - Highly Efficient and Reliable Inverter Concept), H-5 Inverter. (Martino et al., 2012)

Las ventajas más destacadas que ofrecen los generadores sin aislación, son: mayor eficiencia, menor peso y tamaño.

### ANÁLISIS DE LA TOPOLOGÍA SELECCIONADA

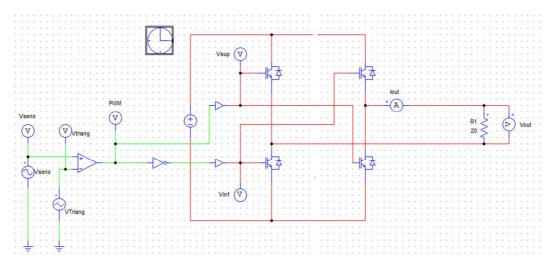

En este trabajo se estudia la etapa CC-CA con una configuración en Puente Completo, Puente H o H-Bridge, (Kumar et al., 2012) utilizando para su análisis el software PSIM, (PSIM, 2010) con el, se puede predecir la forma de onda, amplitud y fase de la señal a inyectar a la red, que luego será contrastada con el prototipo implementado.

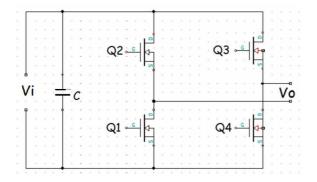

El circuito inversor Puente H, se realiza con cuatro llaves electrónicas que pueden ser transistores del tipo MOSFET(metal-oxide-semiconductor field-effect transistor), estos son apropiados para funcionar en circuitos de conmutación de alta frecuencia. Los mismos poseen tres terminales fuente, drenaje y compuerta.

La disposición de los transistores se observa en la figura 2. La función de este circuito inversor es convertir la tensión de la fuente continua en una onda seno de 220 Volt eficaz, lo que equivale a una tensión máxima instantánea de 311 Volt. Una característica de funcionamiento de este circuito dicta que la tensión de salida no puede ser mayor que la tensión de entrada, por lo tanto la etapa de conversión CC-CC debe entregar una tensión superior a los 311 volt.

Ton 1 Ton 2

A T T T T

Figura 2. Puente H

Figura 3. Señal PWM con dos ciclos de trabajo

La tensión de salida se obtiene activando un transistor por rama. Si se activa Q1 y Q3 se obtiene una tensión positiva en la salida superior de Vo y cuando se activa Q2 y Q4 la polaridad de Vo se invierte.

## MODULACIÓN POR ANCHO DE PULSO

El control de los transistores se realiza utilizando la técnica de modulación por ancho de pulso o (PWM – Pulse Width Modulation), esta técnica consiste en generar una señal rectangular con un período constante en donde se puede variar el ciclo de trabajo de la misma entre 0% y 100%. En la figura 3 se puede ver una señal PWM con dos ciclos de trabajo diferentes, en ella se debe destacar que el período permanece constante. (Mohan et al., 1995)

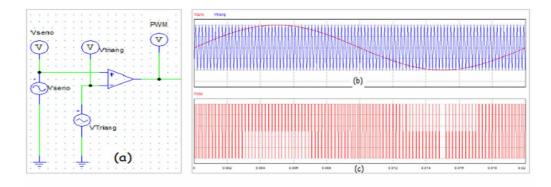

Para generar una señal PWM se puede utilizar un comparador al cual le ingresan una señal portadora diente de sierra y se la compara con una señal moduladora senoidal, ver figura 4. Otro método es crear la señal con un circuito integrado programable. Cualquiera sea la técnica usada se debe destacar que una señal PWM tiene como principal ventaja la obtención de una alta eficiencia de los dispositivos que controla, ya que estos disipan muy poca energía, comparando el funcionamiento de los mismos cuando son controlados en forma lineal. Como desventaja se tiene que los cambios abruptos de estado; encendido-apagado; generan corrientes de conmutación elevadas creando ruido electromagnético o grandes picos de tensión que suelen dañar a los transistores que gobiernan. Para disminuir estas desventajas se suelen utilizar filtros, redes de protección o se utilizan componentes especiales. (García et al., 2006).

Figura 4. (a) Circuito Comparador. (b) Señal diente de sierra y senoidal. (c) Señal PWM

## SIMULACIÓN DE LA ETAPA DE POTENCIA

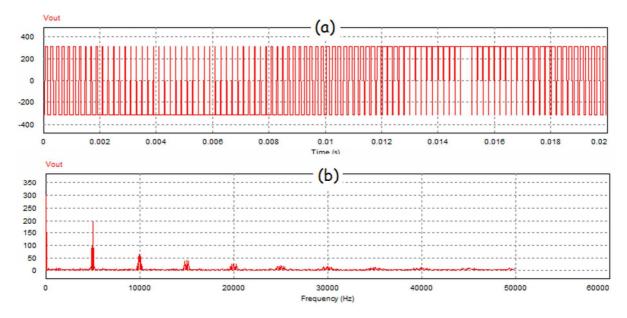

Una vez seleccionado el circuito que se desea implementar, se procedió a su simulación. En la figura 5 se puede observar al mismo, en la figura 6a se tiene la onda de salida para una carga resistiva y en la figura 6b las componentes armónicas del mismo.

Figura 5. Circuito Puente H simulado en Psim.

Figura 6. (a) Señal de salida del Puente H. (b) Contenido armónico de la señal de salida.

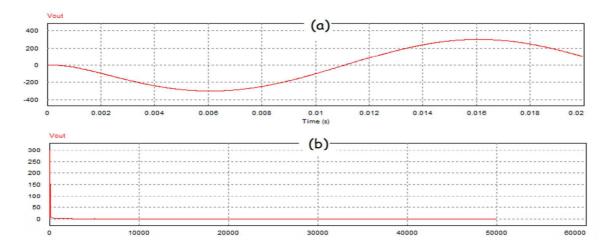

Como se puede ver en la figura 6b, este tipo de circuito tiene un alto contenido armónico. Para mejorar esta situación se procede a incluir un filtro LC, el resultado obtenido se observa en la figura 7.

Figura 7. (a) Señal de salida filtrada del Puente H. (b) bajo contenido armónico

De la simulación se desprende la necesidad de utilizar un filtro a la salida del circuito, en la bibliografía especializada en este tema se encuentran las ecuaciones para obtener los valores de la inductancia y del capacitor.

$$f_c = \frac{1}{2\pi\sqrt{LC}} \tag{1}$$

$$LC = \frac{1}{(2\pi f_c)^2} \tag{2}$$

Realizando los cálculos correspondientes para una frecuencia de corte de 2,5KHz, se obtiene una inductancia L = 22mH y una capacidad C= 11uF. Como en el mercado no se dispone de estos valores en forma standart, lo que se realiza es tomar un valor fijo y conectarlos en forma adecuada hasta obtener el valor deseado. Con la inductancia se procede de igual manera.

### IMPLEMENTACIÓN LA ETAPA DE POTENCIA

Los transistores a utilizar en el armado del circuito puente son (IGBT – Insulated Gate Bipolar Transistor) o también llamados transistor bipolar de compuerta aislada. (Blake et al.) La elección de los mismos se debe a su excelente prestación en conmutación de alta frecuencia que está en el orden de los nano-segundo. Para un correcto funcionamiento esta clase de transistores necesitan un circuito especial que lo comande adecuadamente denominado driver, este controla el encendido y apagado en forma correcta.

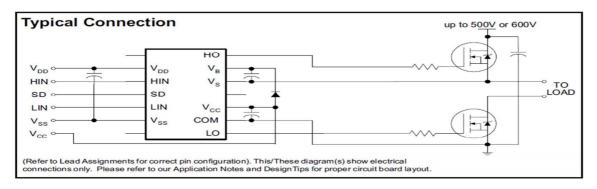

El driver utilizado es el circuito integrado IR2110 de la empresa Intenational Rectifier, (IR2110, 2005). Ver figura 8 En la hoja de datos del fabricante se puede constatar que el número de componentes necesarios para su utilización es mínimo, la tensión de offset es de 500Volt y entrega una corriente de compuerta hasta de 1 Amper. Una característica adicional que tiene el IR2110 es que tanto las entradas como las salidas del mismo son independientes, permitiendo mayor versatilidad en el diseño. (Rivera, 2008) Esta característica mejora al circuito comparador utilizado en la simulación antes presentada, en ella, la señal PWM aplicada a las compuertas de entrada de los transistores están complementadas.

Figura 8. Conexión del Circuito Integrado IR2110.

En los terminales HIN e LIN del driver se conecta la señal que controla a los transistores del circuito puente H.

## CONTROL

El desarrollo del software de control se realiza sobre un micro-controlador de la familia Microhip, el PIC 18F4550, tiene 40 terminales y las características más destacadas se observan en la tabla 1. (Microchip, 2009)

| Micro-<br>controlador | Memoria<br>Programa |                  | Memoria Datos |                |     | 10<br>bit   |                   | SPP | MSSP |                              |            | Timers      |

|-----------------------|---------------------|------------------|---------------|----------------|-----|-------------|-------------------|-----|------|------------------------------|------------|-------------|

|                       | Flash (bytes)       | Single-<br>World | SRAM (bytes)  | EEPROM (bytes) | I/O | A/D<br>(ch) | CCP/ECCP<br>(PWM) |     | SPI  | Master<br>I <sup>2</sup> CTM | Comparador | 8/16<br>Bit |

| PIC18F4550            | 32k                 | 16384            | 2048          | 256            | 35  | 13          | 1/1               | Yes | Y    | Y                            | 2          | 1/3         |

Tabla 1. Características del micro-controlador PIC 18F4550.

El algoritmo implementado contempla el ingreso de señal por los puertos RD3 y RD2, que inician un ciclo de programa, las condiciones que deben cumplir se muestran en la tabla 2.

| RD3 = 1 | Semiciclo positivo     |

|---------|------------------------|

| RD3 = 0 | Semiciclo negativo     |

| RD2 = 1 | Detecta cruce por cero |

Tabla 2. Algoritmo del puerto RD2 y RD3.

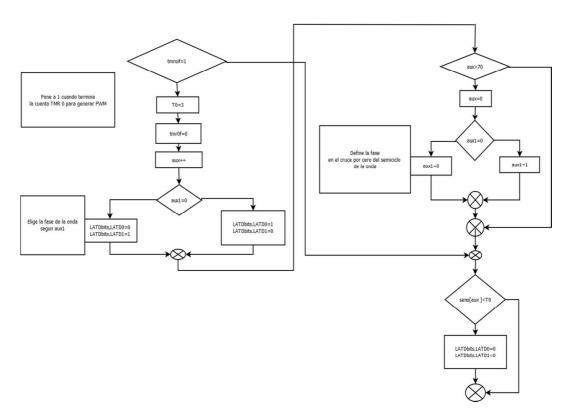

El flujo del programa se puede observar en la figura 9. En él se plasmó los códigos a implementar, como así también la secuencia que era necesario respetar. Se tuvo en cuenta las características del microcontrolador.

Figura 9. Flujo del programa implementado en el micro-controlador PIC 18F4550.

Una vez analizado los códigos se procedió a implementarlos en lenguaje C para ser grabados a posterior en la memoria del micro-controlador. El código se puede observar en la figura 10.

```

#include <p18f4550.b>

#include <timers.h>

#pragma romdata seno=0x3000

//ejecucion

if (aux >= 60)

const rom int

seno[60]={13,26,39,53,65,78,91,103,115

127,138,149,160,170,180,189,198,206,21

LATDbits LATD0=0:

3,220,212,227,232,238,242,246,249,251

while(PORTDbits.RD2=

(aux l==0)

253,254,254,254,253,251,249,246,242,23

{

if(PORTDbits RD3==1)

6.232.227.220.213.206.198.189.180.170.

160,149,138,127,115,103,91,78,66,53,39

aux l=1:

26,13};

auxl=1:

#pragma romdata

#pragma udata

else

extem void _startup(void);

#pragma code

aux 1=0:

RESET_INTERRUPT_VECTOR=0x00

}

0800

WriteTimer0(0);

void_reset(void)

aam goto _startup _endasm

if(seno[aux] < ReadTimer0())

while(1)

pragma code

LATDbits LATD0=0;

if (INTCONbits.TMR0IF=1)

LATDbits LATD1=0:

void main()

WriteTimer0(0)

int aux, aux l anterior=1;

INTCONbits.TMR0IF=0;

if (PORTDbits.RD2=1)&&(anterior=0

// configuration

T0CONbits.TMR0ON=1: //Prende el

TMR0

if (aux l

TOCONbits.TOSBIT=1; // 1=> 8 bits

WriteTimer0(0);

0⇒16 bits

aux=0;

T0CONbits.T0CS=0; // l=> transicion

LATDbits.LATD0=1:

if (aux la

in TOCS bits 0=> clock interno

TOCONbits PSA=0;

LATDbits.LATD1=0;

aux l=1;

asignado 0=> esta asignado

TOCONbits.TOSE=0; // 1⇒ flanco

else

else

ascendente 0=>flanco descemdente

£

T0CONbits.T0PS0=0;

aux 1=0:

LATDbits.LATD0=0:

TOCONbits TOPS 1=1:

T0CONbits.T0PS2=0;

PORTD=0:

anterior=PORTDbits RD2;

LATDbits.LATD1=1:

LATD=0:

TRISDbits TRISD0=0:

}

TRISDbits TRISD1=0:

TRISDbits TRISD2=1:

TRISDbits.TRISD3=1;

```

Figura 10. Código grabado en la memoria del micro-controlador.

## ARMADO DEL PROTOTIPO.

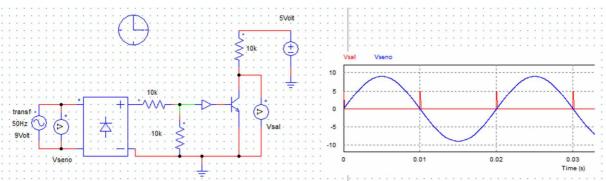

La etapa de detección de cruce por cero, se realizó con el circuito desarrollado por Dogan Ibrahim. (Ibrahim, 2011), se utilizó un transformador reductor de 220Vac a 9Vac, un puente de diodos que alimenta a un circuito de conmutación formado por un transistor NPN. En la figura 11 se observa el circuito empleado con la simulación de la señal obtenida *Vsal*, esta señal se conecta a la puerta RD2 del microcontrolador como se analizó en la sección anterior.

Figura 11. Circuito detector de cruce por cero y señal obtenida mediante simulación.

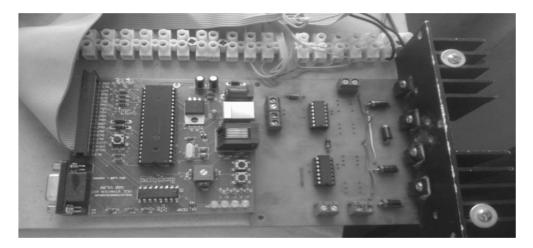

El resto del prototipo se realizó con una placa de entrenamiento de microchip MCE STARTER KIT que se conectó a una placa diseñada y fabricada en el laboratorio de electrónica, esta contiene los circuitos integrados IR2110, y los transistores de salida. El primer prototipo se conectó a transistores Mosfet, alimentados a una tensión de 12Volt, este paso permitió analizar el funcionamiento del sistema: microcontrolador-driver- Mosfet, como se ve en la figura 12, también se pudo observar que la señal de salida obtenida cumplía con los parámetros esperados.

Figura 12. Prototipo en etapa de ensamble: Placa Starter kit con micro controlador, driver IR2110 y transistores Mosfet.

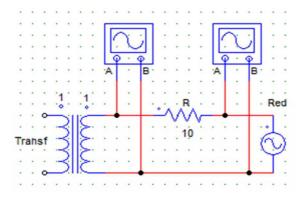

Una vez realizado y ensayado el primer prototipo, se procedió a armar un nuevo puente H con los transistores IGBT IRG4PC50U de la empresa Intenational Rectifier, (IRG4PC50U, 2000) utilizando una fuente de corriente continua de 320 Volt como alimentación. A la salida del puente H se conectó un transformador con relación 1:1 para obtener aislación galvánica con la red eléctrica. Entre el secundario del transformador y la red se colocó una resistencia de 10 ohm que actuaba como protección. El circuito se puede ver en la figura 13.

Figura 13. Conexión de resistencia R de protección entre el transformador de salida del inversor y la red eléctrica.

### RESULTADOS

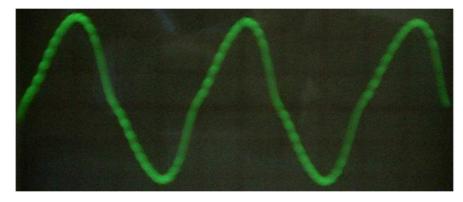

La señal de salida que se obtuvo sobre el secundario del transformador se observa en la figura 14. En ella se puede ver que presenta distorsiones y su forma de onda dista de ser una onda senoidal pura. Esto, puede ser consecuencia de la baja calidad del núcleo del transformador, que unido a las componentes armónicas de la señal generada producen corrientes parásitas en el mismo. El contraste con la onda obtenida en la simulación nos induce a controlar los valores de los elementos del filtro, recordando que se agruparon en serie para obtener el valor calculado, también se debe contemplar un nuevo análisis de la frecuencia de conmutación.

Figura 14. Señal senoidal obtenida.

#### **CONCLUSIONES**

Se analizó en este trabajo la configuración Puente H o Full H-Bridge montado con transistores IGBT. Se realizó la simulación del mismo utilizando el software PSIM, en esta simulación se observó la necesidad de agregar al circuito un filtro para disminuir el contenido armónico debido a la conmutación en alta frecuencia. También se propuso un algoritmo que detecta el cruce por cero de la onda senoidal de la red y también determina si se está en presencia del semiciclo positivo o negativo, estas parámetros son necesarios para una correcta conexión a la red.

Como conclusión general se puede decir que la meta de aprendizaje e implementación se ha cumplido, como trabajo futuro el grupo de investigación se propone corregir y mejorar lo realizado hasta ahora y avanzar en el análisis de nuevas técnicas para la conexión a red, como es la de Multinivel implementada con Puente H, también se va a estudiar e implementar algoritmos que sigan el punto de máxima potencia, para mejor la eficiencia del sistema.

#### REFERENCIAS

- Crossette B. (2011), Estado de la Población Mundial 2011: 7 mil millones de personas su mundo, sus posibilidades. United Nations Population Fund, Capítulo1.

- Renac, (2011). Energía solar fotovoltaica como fuente de energía renovable global. pp 12-13. Renewables Academy AG .

RENAC México.

- Mérida M., Lobón R. y Perles M. (2010). Las plantas fotovoltaicas en el paisaje. Tipificación de impactos y directrices de integración Paisajística. Nimbus, nº 25-26, ISSN 1139-7136, 2010, 129-154.

- Javi V., Serrano V. y Montero M. (2012). Mejoras en un generador fotovoltaico de pequeño porte conectado a red en la zona urbana de salta capital – noroeste argentino. Avances en Energías Renovables y Medio Ambiente Vol. 16, 2012. Impreso en la Argentina. ISSN 0329-5184.

- Javi V., Franco J., Serrano V. y Montero M. (2013). Relevamiento y análisis previos a la instalación de un sistema piloto fotovoltaico conectado a red en el poder judicial de salta como aporte al uso racional de energía y a la promoción de la energía solar. Acta de la XXXVI Reunión de Trabajo de la Asociación Argentina de Energías Renovables y Medio Ambiente. Vol. 1, pp. 07.73-07.80, 2013. Impreso en la Argentina. ISBN 978-987-29873-0-5.

- Kjaer S., Pedersen J. and Blaabjerg F. (2005). A review of single-phase grid-connected inverters For photovoltaic modules. IEEE transactions on industry applications, vol. 41, no. 5, september/october 2005.

- Martino M., Citro C., Rouzbehi K. y Rodriguez P. (2012). Efficiency analysis of single-phase photovoltaic transformer-less inverters. International Conference on Renewable Energies and Power Quality (ICREPQ'12) Santiago de Compostela (Spain), 28th to 30th March, 2012.

- PSIM® User's Guide. (2010). Version 9.0. Release 2. March 2010.

- Mohan N., Undeland T. y Robbins W. (1995). Power eletronics. Converters, applications and design, 2<sup>a</sup> edition, pp 162-163. John Wiley & Sons, inc. New York.

- Kumar V, Mohan N., Manoj M., Naik B., Rao P. (2012). DC-AC full bridge converter, Gokaraju Rangaraju institute of Engineering and Technology, Jawaharlal Nehru Technological University, Hyderabad, 2012.

- García M., Gil G. (2006). Electrónica de Potencia. Componentes, topologías y equipos, capítulo 3. Thompson editores Spain. Blake C. and Chris Bull. IGBT or MOSFET: Choose Wisely. International Rectifier.

- IR2110 (2005). Data Sheet No. PD60147 rev.U. Intenational Rectifier. 2005.

- Rivera I. (2008). Implementación de la técnica de modulación, eliminación selectiva de armónicos. Escuela superior de inge niería mecánica y eléctrica: Adolfo Lopez Mateos. México 2008.

- Microchip. (2009). PIC18F2455/2550/4455/4550. Data Sheet. 28/40/44-Pin, High-Performance, Enhanced Flash, USB Microcontrollers with nanoWatt Technology. Microchip Technology Inc. 2009.

- Ibrahim D. (2011). Accurate Measurement of the Mains Electricity Frequency. ELECO 2011. 7th International Conference on Electrical and Electronics Engineering, 1-4 December, Bursa, TURKEY.

- IRG4PC50U (2000). Data Sheet No. PD91470F. International Rectifier. 2000.

#### ABSTRACT

This paper has as main purpose the analysis of the inverter's power stages, as well as the use of a simulation tool to prove its function and aims to assemble a laboratory prototype comparing its results to the simulated results. It is expected to learn about the use of new technologies in power electronics. First the state of the art of Photovoltaic grid-tie inverters was studied. A topology that could be replicated in the laboratory were selected and subsequently the assembling of it. As a result a senoidal signal of low performance was obtained. The conclusion leads to the acquired knowledge in the management of new electronic components and to improve the obtained results. This paper also proposes to reinforce and deepening the investigation about new technologies.

| <b>Keywords:</b> Photovoltaic grid-tie inverters, simulation, H bridge |  |  |

|------------------------------------------------------------------------|--|--|

|                                                                        |  |  |

| 000000 000000 000 000000000000000000000                                |  |  |

|                                                                        |  |  |